ETM19E-02

# **Application Manual**

# Real Time Clock Module **RX-4575LC**

EPSON TOYOCOM CORPORATION

#### NOTICE

- The material is subject to change without notice.

- Any part of this material may not be reproduced or duplicated in any form or any means without the written permission of Epson Toyocom.

- The information, applied circuit, program, usage etc., written in this material is just for reference. Epson Toyocom does not assume any liability for the occurrence of infringing any patent or copyright of a third party. This material does not authorize the licensing for any patent or intellectual copyrights.

- Any product described in this material may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export licence from the Ministry of International Trade and industry or other approval from another government agency.

- You are requested not to use the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes. You are also requested that you would not make the products available to any third party who may use the products for such prohibited purposes.

- These products are intended for general use in electronic equipment. When using them in specific applications that require extremely high reliability such as applications stated below, it is required to obtain the permission from Epson Toyocom in advance.

- / Space equipment (artificial satellites, rockets, etc) / Transportation vehicles and related (automobiles, aircraft, trains, vessels, etc) / Medical instruments to sustain life / Submarine transmitters

- / Power stations and related / Fire work equipment and security equipment / traffic control equipment / and others requiring equivalent reliability.

- In this manual for Epson Tyocom, product code and marking will still remain as previously identified prior to the merger.Due to the on going strategy of gradual unification of part numbers, please review product code and marking as they will change during the course of the coming months. We apologize for the inconvenience, but we will eventually have a unified part numbering system for Epson Toyocom which will be user friendly.

# CONTENTS

| 1. Overview                                                                   | 1                                                 |

|-------------------------------------------------------------------------------|---------------------------------------------------|

| 2. Block Diagram                                                              | 1                                                 |

| <ul> <li>3. Terminal Discription</li> <li>3.1. Terminal Connections</li></ul> | 2                                                 |

| 5. Recommended Operating Conditions                                           | 3                                                 |

| 6. FrequencyCharacteristics                                                   | 3                                                 |

| <ul> <li>7. Electrical Characteristics</li></ul>                              | 4                                                 |

| <ol> <li>Overview of Functions and Description of Registers</li></ol>         | 6                                                 |

| <ul> <li>9. Description of Functions</li></ul>                                | 8<br>13<br>18<br>21<br>22<br>23<br>27<br>28<br>28 |

| 10. Reference information                                                     | 30                                                |

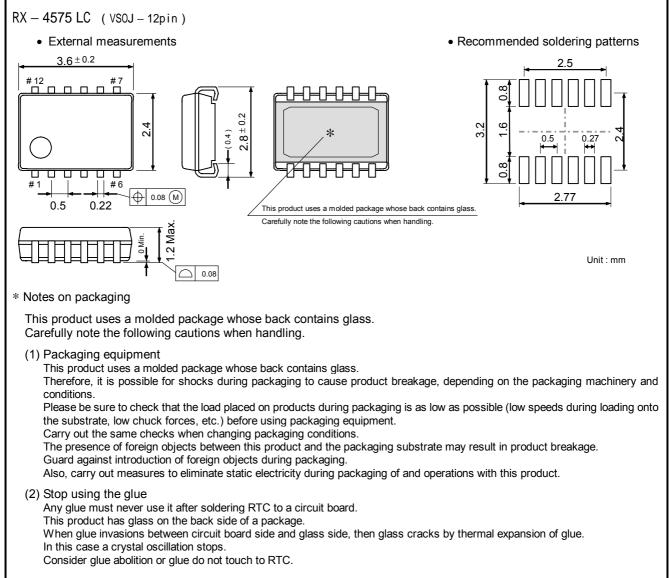

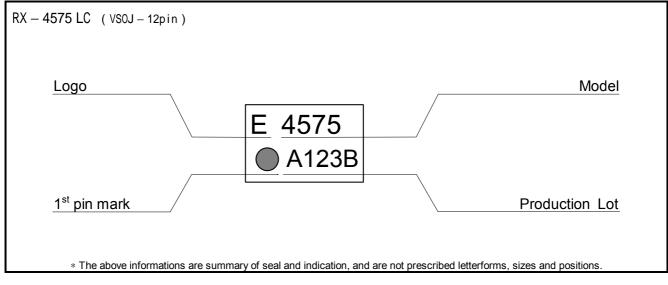

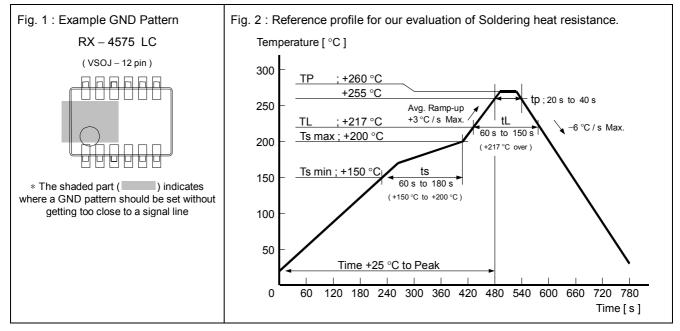

| <ul> <li>11. External measurements / Marking layout</li></ul>                 | 31<br>31                                          |

| 12. Application notes                                                         | 32                                                |

Small-Sized Real Time Clock Module with Event Detecting Function

# **RX – 4575 LC**

- Interface system

- Interface voltage range

- Clock (holding) voltage range

- Backup electricity consumption

- External event detecting function

- : 0.32  $\mu A$  / 3 V ( Typ. )

: 3-wire serial interface

: 1.6 V ~ 5.5 V : 1.3 V ~ 5.5 V

- : In addition to chattering absorbing rate, it is able to set positive logic and negative logic.

- 32.768 kHz output function

- : C-MOS output with output control function

• Real time clock function Clock / Various interrupt functions such as full auto calendar, alarm, timer, external input detection etc.

## 1. Overview

This is a serial interface system real time clock RTC with a built-in precision crystal unit with 32.768kHz. Equipped with 2 chattering-free signal input port, which is able to detect various event such as switch input, interrupt signal etc. correctly to implement interrupt information to CPU. Further, it has various functions such as alarm, timer interrupt built-in based on auto-calendar clock function so that it makes great contribution to optimization and increasing efficiency to distribute system resource.

Device is designed taking low current consumption into consideration based on C-MOS process, and therefore it is the most suitable to apply to small-sized electronic equipment such as DSC, PDA, handy-terminal etc. which are required long period battery backup.

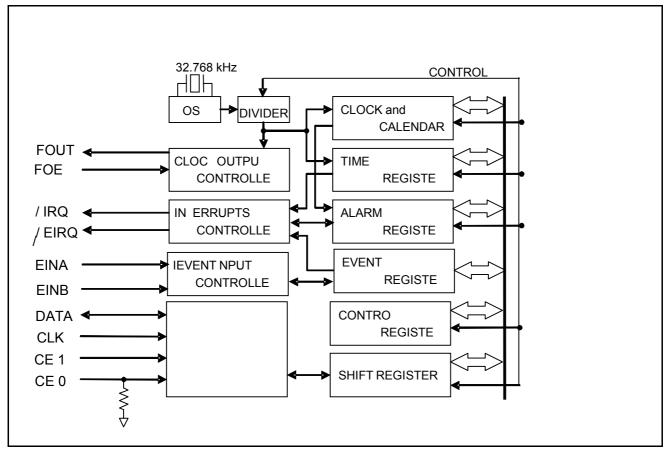

# 2. Block Diagram

# 3. Terminal Discription

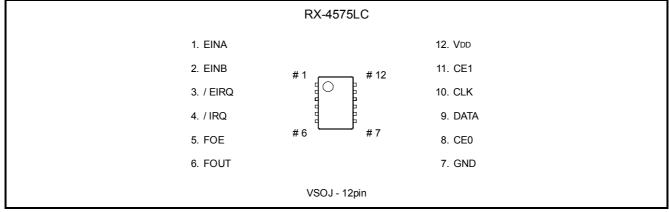

## 3.1. Terminal Connections

#### 3.2. Pin Function

| Signal<br>Name | Input/<br>Output   | Functions                                                                                                                                                                                                                                |

|----------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

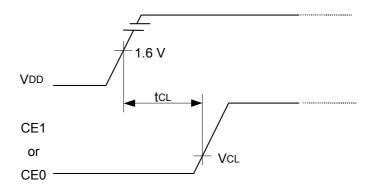

| CE0            | Input              | Chip enabled 0 input pin with built-in pull-down resistors.<br>When both CE0 and CE1 pins are at the "H" level, accessable to the RTC.                                                                                                   |

| CE1            | Input              | This is a chip enabled 1 input pin.<br>When both CE0 and CE1 pins are at the "H" level, accessable to the RTC.                                                                                                                           |

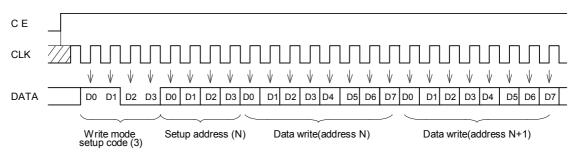

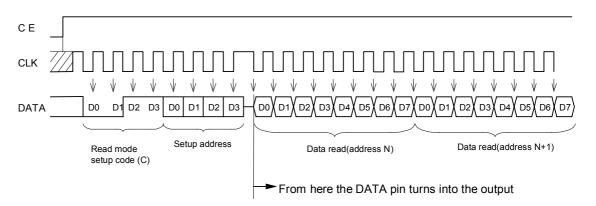

| CLK            | Input              | Shift clock input pin for serial data transfer.<br>During write mode, takes data from DATA pin with CLK signal rising edge, and output<br>data from DATA pin with falling edge during read mode.                                         |

| DATA           | Bi-<br>directional | Data input/output pin for serial data transfer.<br>By setting of mode after input of CE0 or CE1 rising, it is able to apply to input or output pin.                                                                                      |

| EINA           | Input              | It is able to detect input of logic signal.<br>It is able to select Hi detection, Low detection, pullup resistance option and pulldown option by<br>means of register setting. When detect input, it is able to output interrupt signal. |

| EINB           | Input              | It is able to detect input of logic signal.<br>It is able to select Hi detection, Low detection, pullup resistance option and pulldown option by<br>means of register setting. When detect input, it is able to output interrupt signal. |

| FOUT           | Output             | Output pin with 32.768kHz with output control function by FOE input pin and FE bit.<br>With C-MOS output, it is high impedance condition in case output is off,.                                                                         |

| FOE            | Input              | If one of FOE pin or FE bit is "H", 32.768kHz is output from FOUTpin.<br>If both FOE pin and FE bit are "L", FOUT pin is in high impedance condition.                                                                                    |

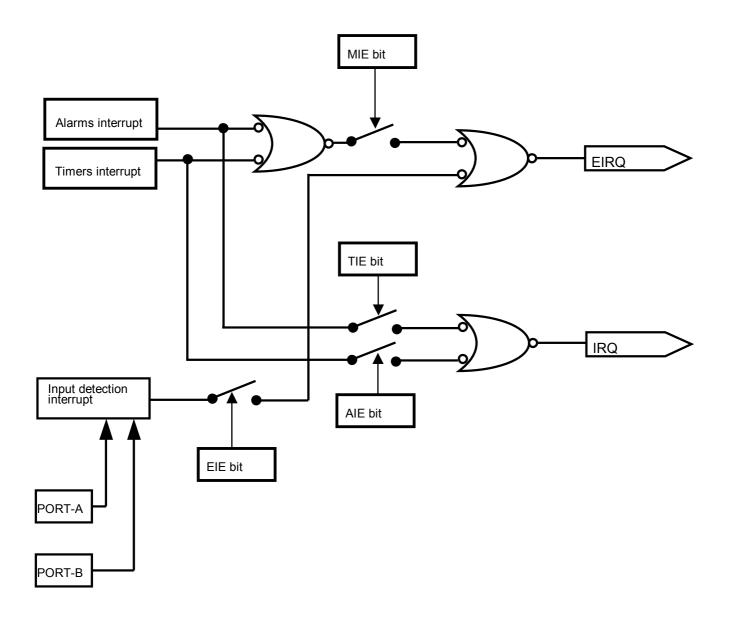

| / EIRQ         | Output             | Open drain output pin for event detecting interrupt.<br>It is also able to output alarm and interrupt timer.                                                                                                                             |

| / IRQ          | Output             | Open drain output pin for alarm and timer interrupt.                                                                                                                                                                                     |

| Vdd            | -                  | Connect to the plus side of power.                                                                                                                                                                                                       |

| GND            | _                  | Copnnect to the ground.                                                                                                                                                                                                                  |

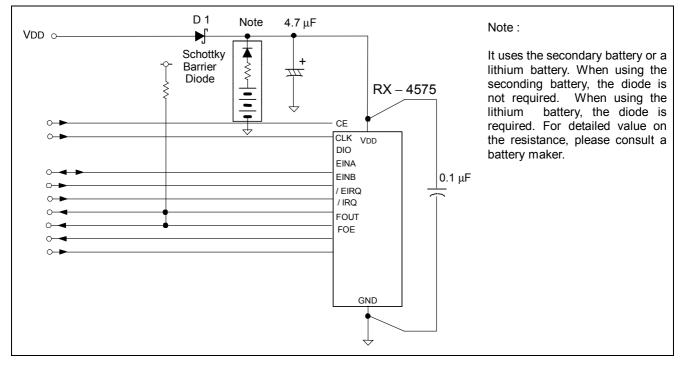

Note : Be sure to connect a bypass capacitor rated at least 0.1  $\mu F$  between VDD and GND.

# 4. Absolute Maximum Ratings

GND = 0V

| Item                | Symbol | Condition                           | Rating            | Unit |

|---------------------|--------|-------------------------------------|-------------------|------|

| Supply voltage      | Vdd    | -                                   | -0.3 ~ +7.0       | V    |

| Input voltage       | Vin    | Input pin                           | GND-0.3 ~ VDD+0.3 | V    |

| Output voltage (1)  | Vout1  | Pullup voltage of / IRQ, / EIRQ pin | GND-0.3 ~ +8.0    | V    |

| Output voltage (2)  | Vout2  | FOUT, DATA                          | GND-0.3 ~ VDD+0.3 | V    |

| Storage temperature | Tstg   | Separated storage without packing   | -55 ~ +125        | ٦°   |

# 5. Recommended Operating Conditions

|                          |        |                 |      |      |      | GND = 0V |

|--------------------------|--------|-----------------|------|------|------|----------|

| Item                     | Symbol | Condition       | Min. | Тур. | Max. | Unit     |

| Operating supply voltage | Vdd    | _               | 1.6  | 3.0  | 5.5  | V        |

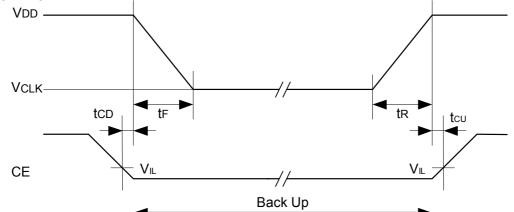

| Clock supply voltage     | Vclk   | _               | 1.3  | 3.0  | 5.5  | V        |

| Operating temperature    | Topr   | No condensation | -40  | +25  | +85  | ٦°       |

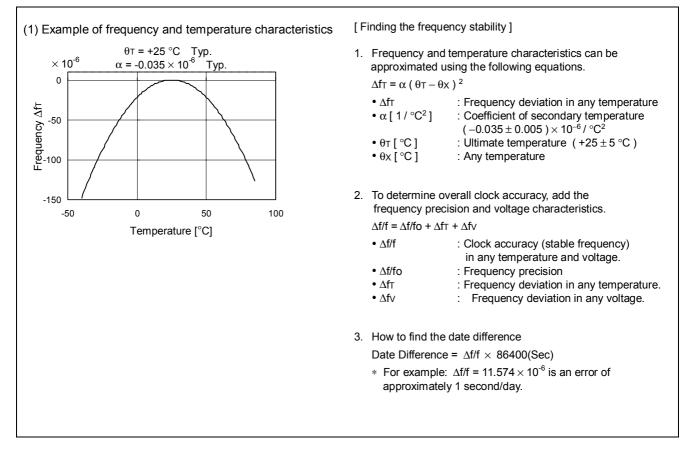

# 6. FrequencyCharacteristics

GND = 0V

|                                       |         |                                                         |                                        | GND = 0V                  |

|---------------------------------------|---------|---------------------------------------------------------|----------------------------------------|---------------------------|

| Item                                  | Symbol  | Condition                                               | Rating                                 | Unit                      |

| Frequency precision                   | Δ f / f | Ta = +25 °C,<br>VDD = 3.0 V                             | 5 ± 23 <sup>(*1)</sup> <sup>(*2)</sup> | × 10 <sup>-6</sup>        |

| Frequency/voltage characteristics     | f / V   | Ta = +25 °C,<br>VDD = 2.0 V ~ 5.0 V                     | ±2 Typ.                                | imes 10 <sup>-6</sup> / V |

| Frequency/temperature characteristics | Тор     | Ta = -20 °C ~ +70 °C,<br>VDD = 3.0 V ; +25 °C reference | +10 / -120                             | × 10 <sup>-6</sup>        |

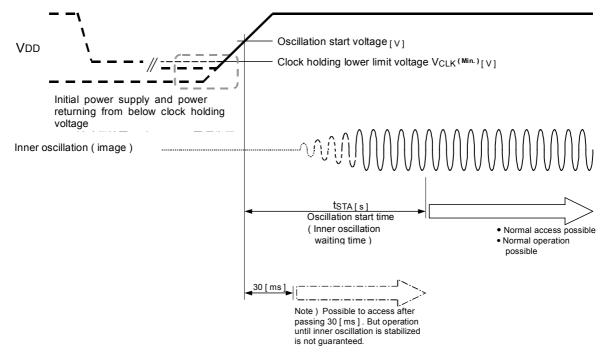

| Oscillation start time                | t sta   | Ta = +25 °C,<br>VDD = 1.6 V                             | 1 Max.                                 | s                         |

|                                       | LSTA    | Ta = - 40 °C ~ +85 °C<br>VDD = 1.6 V                    | 3 Max.                                 | S                         |

| Aging                                 | fa      | Ta = +25 °C,<br>Vod = 3.0 V ; firast year               | $\pm 5$ Max.                           | ×10 <sup>-6</sup> / year  |

$^{\ast 1\,)}$  This difference is 1 minute by 1 month. (excluding offset )

\*2) Including the frequency variation arising from two reflow processing's

\*: Reflow processing as conducted under Epson's conditions (Refer to the individual I specification).

# 7. Electrical Characteristics

#### 7.1. DC characteristics

| * Unless otherwise specified, | GND = 0 V , VDD = 1.6 V to 5.5 V |

|-------------------------------|----------------------------------|

|                               | Ta = _40 °C to +85 °C            |

| 7.1. DC chara               | CICHSUCS         |                                                                      |                                                                                        |           |               | , Т  | <u>′a = –40 °C to</u> | ) +85 °C |

|-----------------------------|------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------|---------------|------|-----------------------|----------|

| Item                        | Symbol           | C                                                                    | Condition                                                                              | Min.      | Тур.          | Max. | Unit                  |          |

| Current<br>consumption (1)  | I <sub>DD1</sub> | CEO,CE1,CLK,EINA,EIN<br>DATA,IRQ,EIRQ=VDD<br>FOUT Output OFF(Hi-Z    |                                                                                        | VDD = 5 V |               | 0.45 | (0.9)                 | μA       |

| Current<br>consumption (2)  | I <sub>DD2</sub> | Event detection OFF<br>REA,REB,EA,EB bit="(                          |                                                                                        | Vdd = 3 V |               | 0.32 | (0.7)                 | μΑ       |

| Current<br>consumption (3)  | I <sub>DD3</sub> | FOE, DATA, IRQ, EIRQ=VD                                              | CEO,CE1,CLK,EINA,EINB=VSS<br>FOE,DATA,IRQ,EIRQ=VDD<br>FOUT Output ON(32.768kHz),CL=0pF |           |               | 3.0  | (7.5)                 |          |

| Current<br>consumption (4)  | I <sub>DD4</sub> | Event detection 7.8m<br>REA,REB bit="0"<br>HLA,HLB,EA,EB,TO,T1       | ns operation                                                                           | VDD = 3 V |               | 1.7  | (4.5)                 | μΑ       |

| Current<br>consumption (5)  | I <sub>DD5</sub> | CEO,CE1,CLK,EINA,EIN<br>FOE,DATA,IRQ,EIRQ=VD<br>FOUT Output ON(32.76 | D                                                                                      | Vdd = 5 V |               | 8.0  | (20.0)                |          |

| Current<br>consumption (6)  | I <sub>DD6</sub> | Event detection 7.8m<br>REA,REB bit="0"<br>HLA,HLB,EA,EB,T0,T1       | ns operation                                                                           | VDD = 3 V |               | 5.0  | (12.0)                | μA       |

| High-level                  | VIH1             | CEO, CE1, CLK, DA<br>EINA, EINB pins                                 | TA, FOE                                                                                |           | 0.7 	imes VDD |      | VDD + 0.3             | V        |

| input voltage               | V1H2             | Pullup voltage of                                                    | /EIRQ, /IRQ                                                                            | pins      |               |      | 6.0                   | V        |

| Low-level<br>input voltage  | Vil              | CEO, CE1, CLK, DA<br>EINA, EINB pins                                 | TA, FOE                                                                                |           | GND - 0.3     |      | 0.3 	imes VDD         | V        |

|                             | V0H1             |                                                                      | VDD = 5 V, IOH                                                                         | = -1 mA   | 4.5           |      | 5.0                   |          |

| High-level VOH2             |                  | DATA, FOUT pins                                                      | = -1 mA                                                                                | 2.2       |               | 3.0  | V                     |          |

|                             | Vонз             | -                                                                    | VDD = 3 V, IOH                                                                         | = –100 μA | 2.9           |      | 3.0                   |          |

|                             | V0L1             |                                                                      | VDD = 5 V, IOL                                                                         | = 1 mA    | GND           |      | GND+0.5               |          |

|                             | Vol2             | DATA, FOUT pins                                                      | VDD = 3 V, IOL                                                                         | = 1 mA    | GND           |      | GND+0.8               | V        |

| Low-level<br>output voltage | Vol3             |                                                                      | VDD = 3 V, IOL                                                                         | = 100 μA  | GND           |      | GND+0.1               |          |

|                             | Vol4             | /EIRQ and                                                            | VDD = 5 V, IOL                                                                         | = 1 mA    | GND           |      | GND+0.25              | V        |

|                             | Vol5             | / IRQ pins                                                           | VDD = 3 V, IOL                                                                         | = 1 mA    | GND           |      | GND+0.4               | V        |

| Input resistance (1)        | RDWN1            | CEO pin                                                              | VDD=5V                                                                                 |           | 75            | 150  | 300                   | k        |

| Input resistance<br>(2)     | RDWN2            | VIN=VDD                                                              | VDD=3V                                                                                 |           | 150           | 300  | 600                   | k        |

| Input resistance (3)        | RDWN3            | EINA,EINB pins                                                       | VDD=5V                                                                                 |           | 15            | 30   | 60                    | k        |

| Input resistance<br>(4)     | RDWN4            | VIN=VDD                                                              | VDD=3V                                                                                 |           | 30            | 60   | 120                   | k        |

| Input resistance<br>(5)     | RUP1             | EINA、EINB pins                                                       | VDD=5V                                                                                 |           | 15            | 30   | 60                    | k        |

| Input resistance<br>(6)     | RUP2             | VIN=VSS                                                              | VDD=3V                                                                                 |           | 30            | 60   | 120                   | k        |

| Input<br>leakage current    | Ilk              | CEO pin ; VIN = GND<br>CE1, CLK, FOE, EIN<br>pins ; VIN = VDD or (   | -0.5                                                                                   |           | 0.5           | μA   |                       |          |

| Output<br>leakage current   | loz              | DATA, / EIRQ, / IR<br>Vout = Vdd or GND                              | Q, FOUT oins,                                                                          |           | -0.5          |      | 0.5                   | μA       |

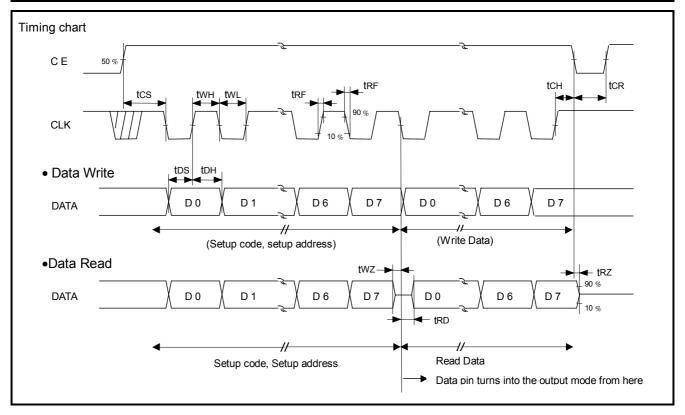

#### 7.2 AC characteristics

| * Unless otherwise specified, G | SND = 0 V , Ta = -40 °C to +85 °C |

|---------------------------------|-----------------------------------|

|---------------------------------|-----------------------------------|

| ltem                                       | Symbol           | Condition                | V <sub>DD</sub> : | = 3 V ± |      | VDD  | Unit |      |      |

|--------------------------------------------|------------------|--------------------------|-------------------|---------|------|------|------|------|------|

| item                                       | Symbol           | Condition                | Min.              | Тур.    | Max. | Min. | Тур. | Max. | Unit |

| CLK clock cycle                            | t <sub>CLK</sub> |                          | 600               |         |      | 350  |      |      | ns   |

| CLK H pulse width                          | t <sub>WH</sub>  |                          | 300               |         |      | 175  |      |      | ns   |

| CLK L pulse width                          | tw∟              |                          | 300               |         |      | 175  |      |      | ns   |

| CE setup time                              | t <sub>CS</sub>  |                          | 300               |         |      | 175  |      |      | ns   |

| CE hold time                               | t <sub>CH</sub>  |                          | 300               |         |      | 175  |      |      | ns   |

| CE recovery time                           | t <sub>CR</sub>  |                          | 400               |         |      | 300  |      |      | ns   |

| Write data setup time                      | t <sub>DS</sub>  |                          | 75                |         |      | 50   |      |      | ns   |

| Write data hold time                       | t <sub>DH</sub>  |                          | 75                |         |      | 50   |      |      | ns   |

| Write data disable time                    | $t_{WZ}$         |                          | 0                 |         |      | 0    |      |      | ns   |

| Read data delay time                       | t <sub>RD</sub>  | CL = 50 pF               |                   |         | 300  |      |      | 120  | ns   |

| Output disable time                        | t <sub>RZ</sub>  | CL = 50 pF<br>RL = 10 kΩ |                   |         | 200  |      |      | 100  | ns   |

| Input rise/fall time                       | t <sub>RF</sub>  |                          |                   |         | 100  |      |      | 50   | ns   |

| FOUT duty<br>( when output at 32.768 kHz ) | tw/t             | 50 % VDD Level           | 45                |         | 55   | 45   |      | 55   | %    |

# 8. Overview of Functions and Description of Registers

#### 8.1 Overview of Functions

#### 1) Clock functions

This function is used to set and read out month, day, hour, date, minute, second, and year (last two digits) data. Any (two-digit) year that is a multiple of 4 is treated as a leap year and calculated automatically as such until the year 2099.

\* For details, see "9.1. Description of Registers".

#### 2) Fixed-cycle interrupts generation function

The fixed-cycle timer interrupt generation function generates an interrupt event periodically at any fixed cycle set between 244.14  $\mu$ s and 4095 minutes.

When an interrupt event is generated, in addition to interrupt hardware with LOW driving of the /IRQ pin, it is also able to detect software detection by read out judgment of timer flag bit.

This function can be selected from two types of operations (single-shot operations and repeated operations).

\* For details, see "9.2. Fixed-cycle Interrupt Function". .

#### 3) Alarm interrupt function

The alarm interrupt generation function generates interrupt events for alarm settings such as date, hour, and minute settings.

When an interrupt event is generated, in addition to interrupt hardware with LOW driving of the /IRQ pin, it is also able to detect software detection by read out judgment of timer flag bit.

\* For details, see "9.3. Fixed-cycle Interrupt Function". .

#### 4) Clock output function

A clock with the same frequency (32.768 kHz) as the built-in crystal resonator can be output from the FOUT pin (CMOS output).

It is also possible to control output with both hardware and software in combination with FOEpin and FE bit.

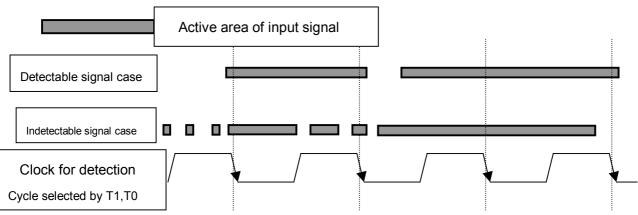

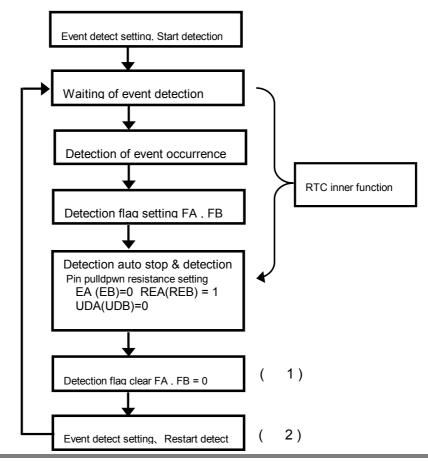

#### 5) Event detecting function

By having 2 logic input pins from outside, it is able to detect each event input.

When detect event, it is able to detect software by read out judgment of each event flag bit in addition to hardware interrupt with LOW driving of the/ ERQ pin.

Each event input pin is able to select optionally pullup and pulldown resistance individually, and is possible to do selecting set positive logic and negative logic respectively.

It is able to set filtering time of chattering from approx. 7.8ms to 125ms by reguster setting.

After detecting event, control input through current and detection operation current to continue internal pulldown resistance immediately and stop detection operation automatically.

Input condition of each event input pin is able to get software monitoring in a real-time through register bit.

\* For details, see [ 9.4. Event detecting function] .

#### 8.2. Register Table

| Address | Functions          | bit 7 | bit 6 | bit 5 | bit 4   | bit 3 | bit 2 | bit 1 | bit 0 | Remarks |

|---------|--------------------|-------|-------|-------|---------|-------|-------|-------|-------|---------|

| 0       | SEC                | fos   | 40    | 20    | 10      | 8     | 4     | 2     | 1     |         |

| 1       | MIN                | fr    | 40    | 20    | 10      | 8     | 4     | 2     | 1     |         |

| 2       | HOUR               | fr    | •     | 20    | 10      | 8     | 4     | 2     | 1     |         |

| 3       | Interrupt Setup    | fr    | MIE   | SB    | SA      | AOF   | TOF   | AQ    | TQ    |         |

| 4       | DAY                | fr    | •     | 20    | 10      | 8     | 4     | 2     | 1     |         |

| 5       | MONTH              | fr    | •     | •     | 10      | 8     | 4     | 2     | 1     |         |

| 6       | YEAR               | 80    | 40    | 20    | 10      | 8     | 4     | 2     | 1     |         |

| 7       | MIN Alarm          | AE    | 40    | 20    | 10      | 8     | 4     | 2     | 1     |         |

| 8       | HOUR Alarm         | AE    | •     | 20    | 10      | 8     | 4     | 2     | 1     |         |

| 9       | DAY Alarm          | AE    | •     | 20    | 10      | 8     | 4     | 2     | 1     |         |

| А       | Input setup        | T1    | то    | HLB   | HLA     | UDB   | REB   | UDA   | REA   |         |

| В       | Event Detection    | EIE   | EB    | EA    | •       | •     | •     | FB    | FA    |         |

| С       | Timer Setup        | TE    | FE    | TD1   | TD0     | 2048  | 1024  | 512   | 256   |         |

| D       | Timer Counter      | 128   | 64    | 32    | 16      | 8     | 4     | 2     | 1     |         |

| E       | Control Register 1 | •     | •     | •     | TI / TP | AF    | TF    | AIE   | TIE   |         |

| F       | Control Register 2 | •     | TEST  | 0     | RESET   | HOLD  | •     | •     | •     |         |

Not When after the initial power-up or when the result of read out the fos bit is "1", initialize all registers, before using the module.

Be sure to avoid entering incorrect date and time data, as clock operations are not guaranteed when the data or time data is incorrect.

- \*1. When input initial power from 0(V, fos, REA, REB bit is set to "1"and each bit of EIE, AIE, TIE, MIE, TE, FE, TEST, EA, EB, UDA, UDB is cleared to "0".

- \*2. The TEST bit is for our test purpose. Bit 5 t when writing. Bit 5 of register F is always "0" and writing is unavailable.

- \*3. Bit with "• "mark can use as general purpose memory bit, we recommend you to fix to "0" in clock register or to give "0" mask after reading to avoid mismatching of the read values.

# 9. Description of Functions

#### 9.1. Descriptipon of registers

9.1.1. Clock counter (Reg - 0[h] ~ 2[h])

| Address [h] | Funct i on | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit O |

|-------------|------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0           | SEC        | fos   | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 1           | MIN        | fr    | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 2           | HOUR       | fr    | •     | 20    | 10    | 8     | 4     | 2     | 1     |

• Counts [seconds], [minutes] and [hours].

• The data format is BCD format. For example, when the "seconds" register value is "0101 1001" it indicates 59 seconds.

• The fr bit is flag bit that indicates the operation status of the RTC's internal clock counter.

\* Note with caution that writing non-existent time data may interfere with normal operation of the clock counter.

#### 1) [SEC] Register

This counter counts seconds.

Count values are updated in order 00 seconds, 01 second, 02 to 59 seconds, 00 seconds, 01 second, etc.

#### 2) [MIN] Register

This counter counts minutes.

Count values are updated in order 00 minutes, 01 minute, 02 to 59 minutes, 00 minutes, 01 minute, etc.

3) [HOUR] Register

Counter that counts [hours] with the round-the-clock system. Count values are updated in order 00 hours, 01 hour, 02 to 23 hours, 00 hours, 01 hour, etc.

#### 4) fos bit (OSC Flag)

This is a flag bit that retains the result when this RTC's internal oscillation status is detected. If the RTC's internal oscillation is stopped, such as when a drop occurs in the power supply voltage, the value of this bit changes from "0" to "1". If this bit's value is "1" when read, this RTC's data is ignored, in which case all registers should be initialized

before being used.

\* This bit is set (= 1) during the initial power-on.

\* After confirming that this bit's value is "1" when read, be sure to clear this fos bit to zero in preparation for the next detection operation.

5) fr bit ( READ Flag )

This is a read-only flag bit that indicates the clock status when read.

If the clock counter is incremented during a read operation, the value of this bit changes from "0" to "1 ". If this bit's value is "1" when read, it may be due to updating of other clock data, in which case all clock registers should be read again.

\* This fr bit is automatically cleared to zero when the CE0 input pin or CE1 input pin goes to low level.

\* The fr bits in Reg – 1 to 5 all have the same function.

#### 9.1.3. Calendar counter (Reg - 04[h] ~ 06[h])

| Address [h] | Funct ion | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit O |

|-------------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|

| 4           | DAY       | fr    | •     | 20    | 10    | 8     | 4     | 2     | 1     |

| 5           | MONTH     | fr    | •     | •     | 10    | 8     | 4     | 2     | 1     |

| 6           | YEAR      | 80    | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

• The auto calendar function updates all dates, months, and years from January 1, 2001 to December 31, 2099.

• The data format is BCD format. For example, a date register value of "0011 0001" indicates the 31st.

\* Note with caution that writing non-existent date data may interfere with normal operation of the calendar counter.

- 1) [DAY] counter

- This is the date counter.

- Updating condition of this counter varies depending on the month.

- \* A leap year is set whenever the year value is a multiple of four (such as 04, 08, 12, 88, 92, or 96). In February of a leap year, the counter counts dates from "01," "02," "03," to "28," "29," "Mar. 01," etc.

| DAY         | Month                    | Date update pattern       |  |  |  |

|-------------|--------------------------|---------------------------|--|--|--|

|             | 1, 3, 5, 7, 8, 10, or 12 | 01, 02, 03 ~ 30, 31, 01 ~ |  |  |  |

| Write/Read  | 4, 6, 9, or 11           | 01, 02, 03 ~ 30, 01, 02 ~ |  |  |  |

| White/iteau | February in normal year  | 01, 02, 03 ~ 28, 01, 02 ~ |  |  |  |

|             | February in leap year    | 01, 02, 03 ~ 28, 29, 01 ~ |  |  |  |

#### 2) [ MONTH ] counter

- This is the month counter.

- It is updated in order Jan. Feb. Mar.  $\sim$  Dec.Jan. Feb. etc.

#### 3) [YEAR ] counter

- This is the year counter.

- It is updated in order 00, 01, 02  $\sim$  99, 00, 01 etc.

- Any year that is a multiple of four (04, 08, 12, 88, 92, 96, etc.) is handled as a leap year.

#### 9.1.4. Alarm register ( Reg - 7[h] ~ 9[h] )

| Address [h] | Funct ion  | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit O |

|-------------|------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 7           | MIN Alarm  | AE    | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 8           | HOUR Alarm | AE    | •     | 20    | 10    | 8     | 4     | 2     | 1     |

| 9           | DAY Alarm  | AE    | •     | 20    | 10    | 8     | 4     | 2     | 1     |

• The AIE bit and AFT bit can both be set or used when using alarm interrupt function to set interrupt events for dates, hours, minutes, etc.

• When the current time matches the settings in the above alarm registers, the AF bit's value is "1" and the AIRQ pin's status is low so that an alarm can be noticed with software or hardware.

\* For details, see "9.3. Alarm Interrupt Function".

9.1.5. Event detection conuter (Reg - A[h] ~ B[h])

| Address [h] | Function        | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| А           | Input setup     | T1    | Т0    | HLB   | HLA   | UDB   | REB   | UDA   | REA   |

| В           | Event Detection | EIE   | EB    | EA    | •     | •     | •     | FB    | FA    |

• Counter to set operation control, selection of detecting cycle and pullup/down registance option in case of using event-detecting function.

• It is able to output interrupt signal from EIRQ pin when detect from EINA for event detection and each pin of EINA. After detecting, detecting operation is automatically stopped and pulldown resistance is automatically connected. In case of restart detection, reseeting is needed.

When detecting, detecting flag is set according to input pin, so that event detection with software is also possible. \* For details, see "9.4. Event detecting Function".

#### 9.1.6. Down-counter for fixed cycle timer (Reg - C[h] $\sim$ D[h])

| Address [h] | Function      | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------------|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| С           | Timer Setup   | TE    | FE    | TD1   | TD0   | 2048  | 1024  | 512   | 256   |

| D           | Timer Counter | 128   | 64    | 32    | 16    | 8     | 4     | 2     | 1     |

Register to set up operation control, selection of clock cycle for timer and presetting value of timer in case of using timer interrupt function.

\* For details, see "9.2. Event detecting Function".

#### 9.1.7. Control register 1 (Reg - E[h])

| Address [h] | Funct ion          | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit O |

|-------------|--------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| E           | Control Register 1 | •     | •     | •     | TI/TP | AF    | TF    | AIE   | TIE   |

• This register is used to record the result of various interrupt event detection operations, or to control the interrupt signal that is externally output when an interrupt event occurs.

- 1) TI / TP bit (Interrupt Signal Output Mode Select. Interrupt / Periodic )

- When a fixed-cycle timer interrupt event occurs (when the TF bit goes from "0" to 1"), this bit specifies whether the interrupt operation occurs just once or repeatedly. Writing "1" to this bit sets repeated operation.

- Writing "0" to this bit sets single-shot operation.

\* For details, see "9.2. Fixed-cycle Timer Interrupt Function ".

2) AF bit ( Alarm Flag )

This is a flag bit that retains the result when an alarm interrupt event has been detected. When an alarm interrupt event occurs, this bit's value changes from "0" to "1". \* For details, see "9.3. Alarm Interrupt Function".

3) TF bit (Timer Flag)

This is a flag bit that retains the result when a fixed-cycle timer interrupt event has been detected. When a fixed-cycle timer interrupt event occurs, this bit's value changes from "0" to "1". \* For details, see "9.2. Fixed-cycle Timer Interrupt Function ".

4) AIE bit ( Alarm Interrupt Enable )

This bit sets the operation of the /AIRQ interrupt signal when an alarm interrupt event has occurred (the AF bit value changes from "0" to "1").

When a "1" is written to this bit, occurrence of an interrupt event causes a low-level interrupt signal to be output from /IRQ pin.

Writing "0" to this bit prohibits low-level output from the /IRQ pin.

- \* For details, see "9.3. Alarm Interrupt Function".

- 5) TIE bit (Timer Interrupt Enable)

This bit sets the operation of the /IRQ interrupt signal when a fixed-cycle interrupt event has occurred (the TF bit value changes from "0" to "1").

When a "1" is written to this bit, occurrence of an interrupt event causes a low-level interrupt signal to be output from /IRQ pin.

Writing "0" to this bit prohibits low-level output from the /IRQ pin.

\* For details, see "9.2. Fixed-cycle Timer Interrupt Function ".

9.1.8. Control register 2 (Reg - F[h])

| Address [h] | Function           | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------------|--------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| F           | Control Register 2 | 0     | TEST  | 0     | RESET | HOLD  | 0     | 0     | 0     |

• This register is used to control stop and resume operations of the clock and calendar function, etc..

1) TEST bit

This is the manufacturer's test bit.

Always leave this bit value as "0" except when testing.

Be careful to avoid writing to this bit when writing "1" to other bits in this register.

- \* If this bit is inadvertently set (= "1") there is a safety function that auto-clears the TEST bit to zero when the CE0 pin or CE1 pin goes to low level.

- 2) RESET bit

Like the STOP function described above, this bit stops the counter operation and resets the internal counter when its value is less than one second.

Writing "1" to this bit stops the counter's operation and resets the RTC's internal counter when its value is less than one second.

Writing a "0" to this bit or setting the CE0 pin or CE1 pin to low level automatically clears (resets) this bit to zero.

- \* In case of RESET=1, in addition to event detecting function, counter function and almost all other functions are stopped.

- 3) HOLD bit

This bit pauses updating of the clock register. If sets HOLD=1 and read out date and hours data, it is surely able to read well-coordinated data.

Although, clock calendar data writing and taking up are overlapped so it is able to prevent data mismatching. Writing "0" to this bit cancels pause mode (resumes clock updates). When HOLD is returned from "1" to "0", if an internal update has occurred in the meantime, an auto compensation function automatically performs a one-second clock update.

\* Even if the time during which HOLD = "1" is two or more seconds, the auto compensation function only compensates the clock update by one second, so using the HOLD bit for one second or less is

recommended.

#### 4) RESET, HOLD bit settings and operation of functions

| t     | bit  |       | Function |       |      |                 |  |  |  |

|-------|------|-------|----------|-------|------|-----------------|--|--|--|

| RESET | HOLD | Clock | Timer    | Alarm | FOUT | Event Detection |  |  |  |

| 0     | 0    | runs  | runs     | runs  | runs | runs            |  |  |  |

| 0     | 1    | *1    | *2       | stops | runs | runs            |  |  |  |

| 1     | 0    | stops | *3       | stops | runs | stops           |  |  |  |

| 1     | 1    | stops | *3       | stops | runs | stops           |  |  |  |

\*1: If the deviation is within one second, the automatic compensation function will kick in to perform the automatic compensation.

\*2: Runs at source clock other than source clock at 1/60 Hz (1 min).

\*3: Runs when the source clock is at 4096 Hz.

\*4 : Correcting function for taking up with HOLD is also functioned when writing. In case of writing access after HOLD setting, additional correcting for 1 second is executed after finishing access if taking up is occurred during access.

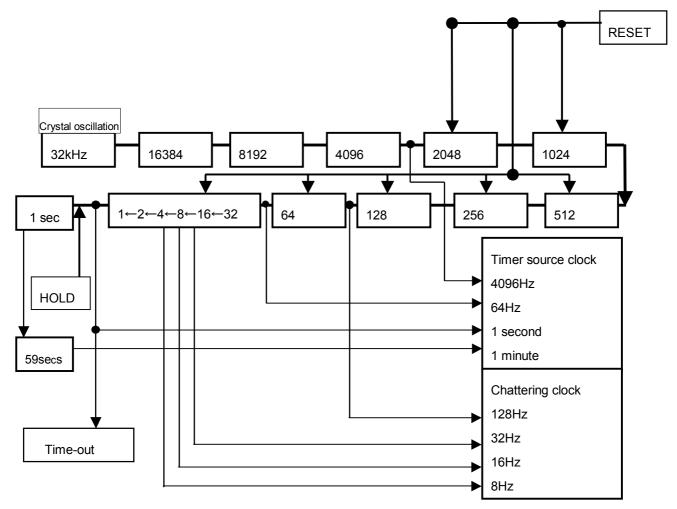

5) RESET, HOLD circuit block image

RESET zero works for resetting from 2048 to 1hz.

For this, not only timer except 4096Hz but also chattering free and time-out are not functioned during RESET. 1Hz clock of timer and time-out are runned even during HOLD but timer 1-minute clock is stopped because HOLD prohibits input signal into 1-minute registers.

Similarly, chattering free function is not affected during HOLD.

#### 9.2. Fixed-cycle Timer Interrupt Function

#### 9.2.1. Fixed-cycle timer interrupt function related register

| Address [h] | Function           | bit 7 | bit 6 | bit 5 | bit 4   | bit 3 | bit 2 | bit 1 | bit 0 |

|-------------|--------------------|-------|-------|-------|---------|-------|-------|-------|-------|

| С           | Timer Setup        | TE    | FE    | TD1   | TD0     | 2048  | 1024  | 512   | 256   |

| D           | Timer Counter      | 128   | 64    | 32    | 16      | 8     | 4     | 2     | 1     |

| E           | Control Register 1 | •     | •     | •     | TI / TP | AF    | TF    | AIE   | TIE   |

\* Before entering settings for operations, we recommend todo "0" clear to the TE and TIE bits to avoid unnecessary interrupt from occurring inadvertently while entering settings.

#### 1) TI / TP bit ( Timer Interrupt / Periodic )

When a fixed-cycle timer interrupt event occurs (TF value changes from "0" to 1"), this bit specifies whether the interrupt operation will be performed only once or repeatedly.

| TI / TP      | Data | Description                                                                                                |

|--------------|------|------------------------------------------------------------------------------------------------------------|

| Write / Read | 0    | [Level interrupt mode]<br>Makes operation of fixed-cycle timer interrupt function only once                |

| White / Read | 1    | [Repeated interrupt mode]<br>Makes continuous operation of fixed-cycle timer interrupt function repeatedly |

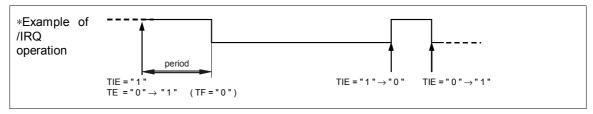

#### \*1) Outline drawing of level interrupt mode (TI/TP = "0")

After an interrupt event occurs, the operation is performed only once.

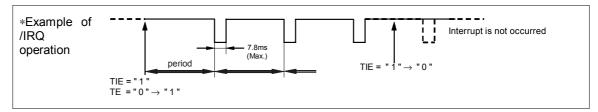

\*2) Outline drawing of repeated interrupt mode (TI/TP = "1")

After an interrupt event occurs, the operation is performed repeatedly.

#### 2) TD1, TD0 bit

These bits specify the fixed-cycle timer interrupt function's countdown period (source clock). Four different periods can be selected via combinations of these two bit values.

| TD1, TD0 | TD1<br>(bit 5) | TDO<br>(bit 4) | Source clock                 | Auto reset time<br>tRTN |

|----------|----------------|----------------|------------------------------|-------------------------|

|          | 0              | 0              | 4096 Hz / Once per 244.14 μs | 122 μs                  |

| W / R    | 0              | 1              | 64 Hz / Once per 15.625 ms   | 7.813 ms                |

| W / K    | 1              | 0              | 1 Hz / Once per second       | 7.813 ms                |

|          | 1              | 1              | 1/60 Hz / Once per minute    | 7.813 ms                |

- \*1) The /IRQ pin's auto reset time (tRTN) varies as shown above according to the source clock setting.

- \*2) An interrupt that occurs when the source clock is in 1/60 Hz mode is linked to the internal clock's "minute" update operation.

\*3) An interrupt that occurs when the source clock is in 1 Hz mode is not linked to the internal clock. (Instead, a dedicated 1 Hz timer circuit is used for independent operation.)

3) Down counter for fixed-cycle timer (Timer Counter)

This register (Reg-D) is used for setting up initial value (pre-setting value) of presettable down counter, and is able to set up optional cpount value from 1 (01 h) ~ 4095 (FFF h).

The counter counts down based on the source clock's period, and when the count value changes from 01h to 00h, the TF bit value becomes "1".

- \*1. When start to read this cpount down, presetting value can always be read. Count value during cound down cannot be read.

- \*2. When the fixed-cycle timer interrupt function is not being used, this register b it can be used as a memory bit. But in such cases, unless stop time with setting to "0" to the TE and TIE, memory value may be changed due to data declimentation or unnecessary interrupt may be occurred.

#### 4) TE bit (Timer Enable)

This bit enables operation of the fixed-cycle timer interrupt function to start.

| TE           | Data | Description                                                                                                                                                                                                                                                                     |

|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 0    | Timer is stopped after reloading presetting valu. It is unable to pausetimer even if set this bit to zero during count down.                                                                                                                                                    |

| Write / Read | 1    | Fixed-cycle timer is counted down.<br>With level interrupt mode, it is zero cleared simultaneously with interrupt<br>occurrence.<br>(Note) During level interrupt mode, the TF bit first should be cleared to zero,<br>then the TE bit value should be changed from "0" to "1". |

#### 5) TF bit (Timer Flag)

This is a flag bit that retains the result when a fixed-cycle timer interrupt event is detected.

The value of this bit changes from "0" to "1" when a fixed-cycle timer interrupt event occurs. If the TIE bit value is "1" at that time, the /IRQ pin goes to low level to indicate that an event has occurred.

| TF         | Data                                                    | Description                                                                                                                                                              |

|------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>Write |                                                         | If execute " 0 " clear, external output of timer interrupt can be cancelled.<br>However, during repeated intrrupt, it is unable to cancel since interrupt time is fixed. |

| 1          | This bit is invalid after a "1" has been written to it. |                                                                                                                                                                          |

|            | 0                                                       | No timer interrupt occurrence.                                                                                                                                           |

| Read       | 1                                                       | Timer interrupt events are detected.<br>* Result is retained until this bit is cleared to zero                                                                           |

#### 6) TIE bit (Timer Interrupt Enable)

This bit sets the operation of the /IRQ interrupt signal when a fixed-cycle timer interrupt event has occurred (TF bit value changes from "0" to "1").

When a "1" is written to this bit, occurrence of an interrupt event causes a low-level interrupt signal to be output from /IRQ pin.

When a "0" is written to this bit, output from the /IRQ pin is prohibited (disabled).

| TIE          | Data | Description                                                                                                                                                                                                                                                                                     |

|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write / Read | 0    | <ol> <li>When a fixed-cycle timer interrupt event occurs, an interrupt signal is not<br/>generated or is canceled (/INT status remains Hi-Z).</li> <li>When a fixed-cycle timer interrupt event occurs, the interrupt signal is<br/>canceled (/INT status changes from low to Hi-Z).</li> </ol> |

|              | 1    | When a fixed-cycle timer interrupt event occurs, an interrupt signal is generated (/INT status changes from Hi-Z to low).                                                                                                                                                                       |

#### 7) FE bit (FOUT Enable)

Bit to control 32768Hz output of FOUT pin.

It is able to control optional output in combination with FOE pin.

| FE           | FE value | FOE pin setting | FOUT pin condition |  |  |

|--------------|----------|-----------------|--------------------|--|--|

|              | 0        | High            | 32768Hz output     |  |  |

| Write / Read | 0        | Low             | Hi-Z               |  |  |

| White / Read | 1 –      | High            | 32768Hz output     |  |  |

|              |          | Low             | 32768Hz output     |  |  |

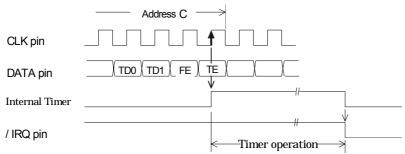

#### 9.2.2. Timer start timing

Counting down of the fixed-cycle timer value starts at the rising edge of the CLK signal that occurs when the TE value is changed from "0" to "1" (after bit 0 is transferred).

#### 9.2.3. Fixed-cycle timer interrupt interval and time error

The combination of the source clock settings (settings in TD1 and TD0) and fixed-cycle timer countdown setting (Reg–C setting) sets the fixed-cycle timer interrupt interval, as shown in the following examples.

| <b>T</b>                 | <b>1</b> | Source clock |           |             |               |  |  |  |  |  |

|--------------------------|----------|--------------|-----------|-------------|---------------|--|--|--|--|--|

| Timer Counter<br>setting |          | 4096 Hz      | 64 Hz     | 1 Hz        | 1/60 Hz       |  |  |  |  |  |

|                          |          | TD1,0=0,0    | TD1,0=0,1 | TD1,0 = 1,0 | TD1,0=1,1     |  |  |  |  |  |

| 0                        | (00h)    | _            | _         | _           | -             |  |  |  |  |  |

| 1                        | (01h)    | 244.14 μs    | 15.625 ms | 1 s         | 1 min         |  |  |  |  |  |

| 2                        | (02h)    | 488.28 μs    | 31.250 ms | 2 s         | 2 min         |  |  |  |  |  |

| 3                        | (03h)    | 732.42 μs    | 46.875 ms | 3 s         | 3 min         |  |  |  |  |  |

| •                        |          | •            | •         | •           | •             |  |  |  |  |  |

| •                        |          | •            | •         | •           | •<br>2day 20h |  |  |  |  |  |

| 4095                     | (FFFh)   | 999.75 ms    | 63.984 s  | 1h8min15s   | 15min         |  |  |  |  |  |

• Fixed-cycle timer interrupts time error and fixed-cycle timer interrupt interval time

A fixed-cycle timer interrupt time error is an error in the selected source clock's  $^{+0}/_{-1}$  interval time. Accordingly, the fixed-cycle timer interrupt's interval (one cycle) falls within the following range in relation to the set time.

Fixed-cycle timer interrupt's interval

(Fixed-cycle timer interrupt's set time( $\ast$ ) – source clock interval) to (fixed-cycle timer interrupt set time)

\*) Fixed-cycle timer interrupt's set time = Source clock setting × Countdown timer setting for fixed-cycle timer

\* The time actually set to the timer is adjusted by adding the time described above to the communication time for the serial data transfer clock used for the setting.

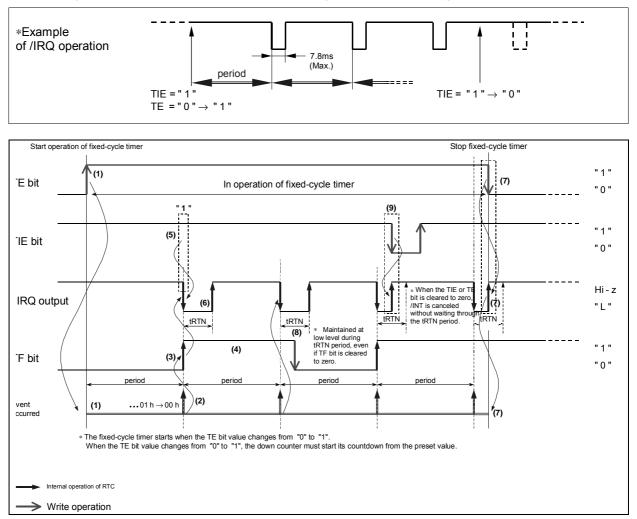

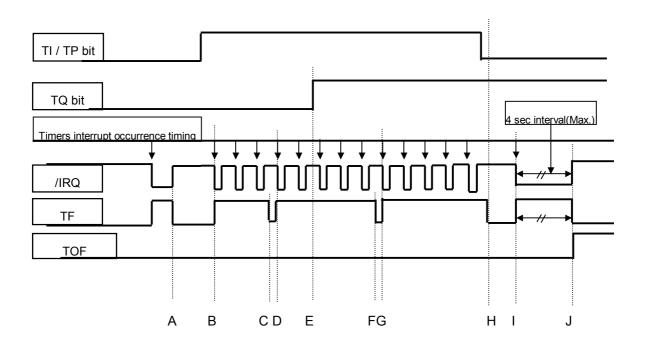

9.2.4. Diagram of fixed-cycle timer interrupt function

IRQ pin concerned, alarms interrupt and timer interrup are OR output.

Hereinafter, explain about timer interrupt on the assumption that no alarm interrupt is occurred.

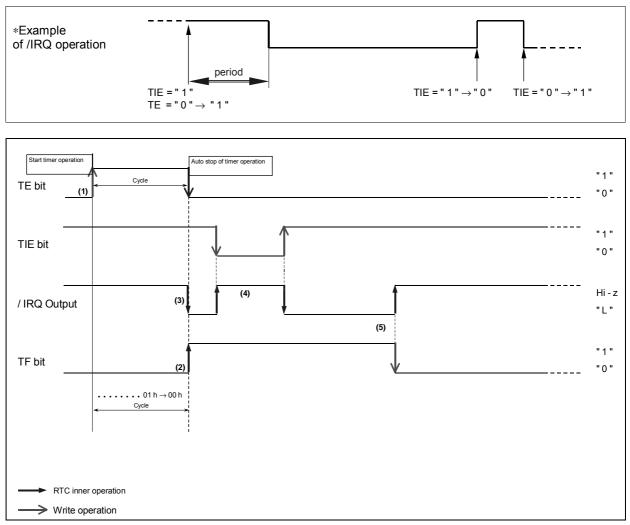

- 9.2.4.1. Level interrupt mode ( TI / TP = " 0 " )

- After an interrupt event has occurred, this function operates only once.

\*) Before using level interrupt mode (TI / TP = "0"), be sure to clear the TE bit and the TF bit to zero each time.

- (1) When a "1" is written to the TE bit, the fixed-cycle timer countdown starts from the preset value.

- (2) A fixed-cycle timer interrupt event starts a countdown based on the countdown period (source clock). When the count value changes from 01h to 00h, an interrupt event occurs. At the same time, TE bit is zero cleared and preset value is loaded by timer cpunter to stop.

- (3) If the TIE bit = "1" when a fixed-cycle timer interrupt occurs, /IRQ pin output goes low. If TIE = "0", /IRQ pin does not output timer interrupt.

- (4) During the period when the TF bit value is "1" following the occurrence of an interrupt event, the TIE bit can be set to switch the /IRQ pin to any status.

- (5) When the TF bit = "1" its value is retained until it is cleared to zero. If TF bit is cleared to " 0 ", output of timer interrupt is stopped.

#### 9.2.4.2 Repeated interrupt mode (TI/TP = "1")

• With set cycle, execution of the operation is automatically repeated continuously.

- (1) When a "1" is written to the TE bit, the fixed-cycle timer countdown starts from the preset value.

- (2) A fixed-cycle timer interrupt event starts a countdown based on the countdown period (source clock). When the count value changes from 001h to 000h, an interrupt event occurs.

- \* After the interrupt event that occurs when the count value changes from 01h to 00h, the counter automatically reloads the preset value and again starts to count down. (Repeated operation)

- (3) When a fixed-cycle timer interrupt event occurs, "1" is written to the TF bit.

- (4) TF bit maintains "1" until it is cleared to zero. (Even if cleare TE bit to zero, TF bnit is not affected.)

- (5) If the TIE bit = "1" when a fixed-cycle timer interrupt occurs, /IRQ pin output goes low.

\* If TIE ="0" when occurred fixed-cycle timer interrupt, timer interrupt does not output to /IRQ.

- (6) Output from the /IRQ pin remains low during the tRTN period following each event, after which it is automatically cleared to Hi-Z status.

\* /IRQ is again set low when the next interrupt event occurs.

- (7) When a "0" is written to the TE bit, the fixed-cycle timer function is stopped and the /IRQ pin is set to Hi-Z status.

- (8) When /IRQ is at low level and the TF is changed from "1" to "0", / IRQ remains at low level and is not reset to Hi-Z status.

- (9) When /IRQ = low, the /IRQ pin status changes from "1" to "0", it changes from /IRQ "L" to Hi-z immediately.

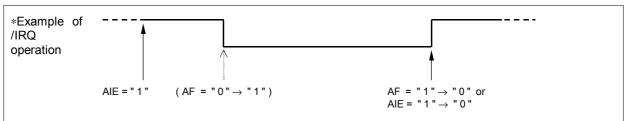

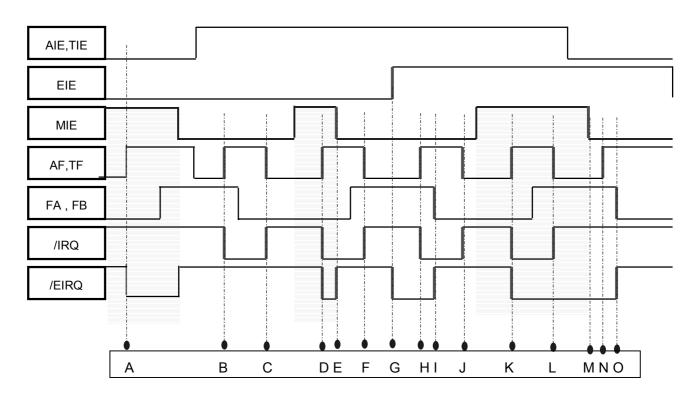

#### 9.3. Alarm Interrupt Function

The alarm interrupt generation function generates interrupt events for alarm settings such as date, day, hour, and minute settings.

When an interrupt event occurs, the AF bit value is set to "1" and the /IRQ pin goes to low level to indicate that an event has occurred.

\* /IRQ pin concerned, alarm interrupt and fixed-cycle timer interrupt execute OR output. Hereinafter, explain about alarm interrupt on the assumption that no fixed-cycle timer interrupt is occurred.

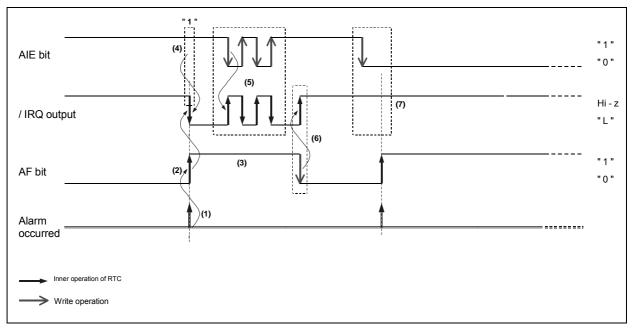

#### 9.3.1. Diagram of alarm interrupt function

- (1) Comparison operation of the date/time and alarm is done with update timing when changed from 59 to 00 sec. Therefore, even if alarm data with the same as the present time is set, alarm will not be given immediately.

- (2) When a time update interrupt event occurs, the AF bit values becomes "1".

- (3) When the AF bit = "1", its value is retained until it is cleared to zero.

- (4) If AIE = "1" when an alarm interrupt occurs, the /IRQ pin output goes low.

- \* When an alarm interrupt event occurs, /IRQ pin output goes low, and this status is then held until it is cleared via the AF bit or AIE bit.

- (5) If the AIE value is changed from "1" to "0" while /IRQ is low, the /INT status immediately changes from low to Hi-Z. After the alarm interrupt occurs and before the AF bit value is cleared to zero, the /IRQ status can be controlled via the AIE bit.

- (6) If the AF bit value is changed from "1" to "0" while /INT is low, the /IRQ status immediately changes from low to Hi-Z.

- (7) If the AIE bit value is "0" when an alarm interrupt occurs, the /IRQ pin status remains Hi-Z.

#### 9.3.2. Alarm interrupt function registers

| Address [h] | Funct i on         | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit O |

|-------------|--------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 1           | MIN                | fr    | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 2           | HOUR               | fr    | •     | 20    | 10    | 8     | 4     | 2     | 1     |

| 4           | DAY                | fr    | •     | 20    | 10    | 8     | 4     | 2     | 1     |

| 7           | MIN Alarm          | AE    | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 8           | HOUR Alarm         | AE    | •     | 20    | 10    | 8     | 4     | 2     | 1     |

| 9           | DAY Alarm          | AE    | •     | 20    | 10    | 8     | 4     | 2     | 1     |

| E           | Control Register 1 | •     | •     | •     | TI/TP | AF    | TF    | AIE   | TIE   |

\* Before entering settings for operations, we recommend writing a "0" to the AIE bit to prevent hardware interrupts from occurring inadvertently while entering settings.

\* When the alarm interrupt function is not being used, the Alarm registers (Reg - 7 to 9) can be used as a RAM register. In such cases, be sure to write "0" to the AIE bit.

\* \* Even when the alarm registers (Reg - 7 to 9) are used as a RAM register, surely set AIE bit to "0" to avoid unnecessary alarm due to conincidence with write data and the present time.

1) Alarm registers (Reg - 7[h] ~ A[h])

Set hour, minute and date to be given alarm.

When the settings made in the alarm registers match the current time, the AF bit value is changed to "1". At that time, if the AIE bit value has already been set to "1", the /IRQ pin goes low.

- \*1) Register set to AE = "1" concerned, it is always functioned as alarm agreement regardlessofdata. (Example) Write 81h (AE = "1") to the DAY Alarm register (Reg - 9): Alarm is given only due to coincidence with hour and minute data because date is always coincidence.

- \*2) When set all 3 AE bits to "1", alarm interrupt is occurred every minute.

- \*3) Comparison of alarm is done in timing when update from 59 to 00 seconds.

- 2) AF bit (Alarm Flag)

This is a flag bit that retains the result when an alarm interrupt event has been detected.

When this flag bit value is already set to "0", occurrence of an alarm interrupt event changes it to "1".

| AF    | Data | Description                                                                                                                               |

|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Write | 0    | The AF bit is cleared to zero to prepare for the next status detection * Clearing this bit to zero enables /IRQ low output to be canceled |

|       | 1    | This bit is invalid after a "1" has been written to it.                                                                                   |

|       | 0    | No alarm interrupt events are detected                                                                                                    |

| Read  | 1    | Alarm interrupt events are detected.<br>* Result is retained until this bit is cleared to zero.                                           |

3) AIE bit ( Alarm IRQ Interrupt Enable )

This bit sets the operation of the /IRQ interrupt signal when an alarm interrupt event occurs (when the TF bit value changes from "0" to "1").

Writing "1" to this bit causes a low-level interrupt signal to be output from the /IRQ pin when an interrupt event occurs.

When a "0" is written to this bit, output from the /IRQ pin is prohibited.

| AIE          | Data | Description                                                                                                                                                                                                                                                |

|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write / Read | 0    | <ol> <li>When an alarm interrupt event occurs, an interrupt signal is not generated<br/>(/IRQ status remains Hi-Z).</li> <li>When an alarm interrupt event occurs, the interrupt signal is canceled<br/>(/IRQ status changes from low to Hi-Z).</li> </ol> |

|              | 1    | When an alarm interrupt event occurs, an interrupt signal is generated (/IRQ status changes from Hi-Z to low).                                                                                                                                             |

\* To detect occurrence of an alarm interrupt event without setting /IRQ to low level, monitor the AF bit value (note when it changes from "0" to "1") while AIE = "0".

#### 9.3.3. Examples of alarm settings

1) Basic information about alarm settings

- Four parameters can be set as alarm objects are the following 3 items: minute, hour, day, and date.

- Hour settings are based on the round -the-clock system.

- Alarm register set AE bit to "1" is always considered alarm coincidence.

If set AE to [date] and set alarm to 22:30 hours, alarms interrupt is occurred at 22:30 hrs every day since date is disregarded.

\* When the AE bit = 1 for all objects (minute, hour, day, and date), an alarm interrupt event is given every minute.

2) Examples of alarm settings are listed below.

|                                                                                                                                                     | Reg - 9                 | Reg - 8                 | Reg - 7                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|

| Examples of alarm settings                                                                                                                          | DAY<br>Alarm            | HOUR<br>Alarm           | MIN<br>Alarm            |

| <u>•Gives alarm on 17<sup>th</sup> day at 07 : 00</u><br>[Dat] 17<br>[Hour] 07AM (round-the-clock<br>system→07hour)<br>[Minute] 00 minute orignored | 17 h                    | 07 h                    | 80h ~ FFh<br>AE = " 1 " |

| • Gives alarm at every minute sharp<br>[Date] Ignored<br>[Hour] Ignored<br>[Minute] Ignored                                                         | 80h ~ FFh<br>AE = " 1 " | 80h ~ FFh<br>AE = " 1 " | 80h ~ FFh<br>AE = " 1 " |

## 9.4. Event detecting functions

9.4.1. Event detection setting register

| Address [h] | Funct i on      | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit O |

|-------------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| А           | Input Setup     | T1    | TO    | HLB   | HLA   | UDB   | REB   | UDA   | REA   |

| В           | Event detection | EIE   | EB    | EA    | •     | •     | •     | FB    | FA    |

9.4.2. Setting bit functions related event detection

| Journy Dit IU |       |                                                                                         |                                                                                                                                                                |  |  |  |

|---------------|-------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Port          | BIT   | Value                                                                                   | Function Specification                                                                                                                                         |  |  |  |

| А             | HLA   | 1                                                                                       | Set EINA pin to Hi input detection mode                                                                                                                        |  |  |  |

| ~             |       | 0                                                                                       | Set EINA pin to Low input detection mode                                                                                                                       |  |  |  |

|               |       | 1                                                                                       | Set EINB pin to Hi input detection mode                                                                                                                        |  |  |  |

| В             | HLB   | 0                                                                                       | Set EINB pin to Low input detection mode                                                                                                                       |  |  |  |

|               |       | 1                                                                                       | Inner resistance of EINA pin concerned, pullup side is effective.                                                                                              |  |  |  |

|               |       | 0                                                                                       | Inner resistance of EINA pin concerned, pulldown side is effective                                                                                             |  |  |  |

|               | UDA   |                                                                                         | If detect input of EINA pin, UDA bit is automatically cleared to                                                                                               |  |  |  |

|               |       |                                                                                         | zero to make pulldown resistance effect. After input initial power,                                                                                            |  |  |  |

|               |       |                                                                                         | keeps zero clear condition.                                                                                                                                    |  |  |  |

| Α             |       | 1                                                                                       | Connect inner pullup/pulldown resistance to EINA pin.                                                                                                          |  |  |  |

|               |       | 0                                                                                       | Release inner pullup/pulldown resistance of EINA pin                                                                                                           |  |  |  |

|               | REA   |                                                                                         | nput of EINA pin, REA bit is automatically set and make a                                                                                                      |  |  |  |

|               | REA   |                                                                                         | istance to ON.                                                                                                                                                 |  |  |  |

|               |       |                                                                                         | t initial power, keeps set condition. In case a buil-in resistance is not used,<br>urrent is occurred if port input become to open and current consumption may |  |  |  |

|               |       |                                                                                         | sed substantially.                                                                                                                                             |  |  |  |

|               |       | 1                                                                                       | Inner resistance of EINB pin concerned, pullup side is effective.                                                                                              |  |  |  |

|               |       | 0                                                                                       | Inner resistance of EINB pin concerned, pulldown side is effective.                                                                                            |  |  |  |

|               | UDB   | If detect in                                                                            | nput of EINB pin, UDB bit is automatically cleared to zero to                                                                                                  |  |  |  |

|               |       |                                                                                         | down effect. After input initial power,                                                                                                                        |  |  |  |

|               |       |                                                                                         | o clear condition.                                                                                                                                             |  |  |  |

| В             | REB   | 1                                                                                       | Connect inner pullup/pulldown resistance to EINB pin.                                                                                                          |  |  |  |

|               |       | 0                                                                                       | Release inner pullup/pulldown resistance of EINB pin.                                                                                                          |  |  |  |

|               |       | If detect input of EINB pin, REB is automatically set to make a built-in Resistance ON. |                                                                                                                                                                |  |  |  |

|               |       |                                                                                         | e ON.<br>t initial power, keeps set condition. In case a buil-in resistance is not used,                                                                       |  |  |  |

|               |       |                                                                                         | urrent is occurred if port input become to open and current consumption may                                                                                    |  |  |  |

|               |       |                                                                                         | sed substantially.                                                                                                                                             |  |  |  |

|               |       | 1                                                                                       | Input to EINA pin is detected.                                                                                                                                 |  |  |  |

| Α             | FA    | l                                                                                       | After setting, keeps "1" until 0-write.                                                                                                                        |  |  |  |

|               |       | 0                                                                                       | No input to EINA p;in.                                                                                                                                         |  |  |  |

|               | -     | 1                                                                                       | Input to EINB pin is detected.                                                                                                                                 |  |  |  |

| В             | FB    |                                                                                         | After setting, keeps "1" until 0-write.                                                                                                                        |  |  |  |

|               |       | 0                                                                                       | No input to EINB pin.                                                                                                                                          |  |  |  |

|               |       | 1                                                                                       | Do detecting operation of EINA pin.                                                                                                                            |  |  |  |

|               |       | 0<br>If detect in                                                                       | Stop detection of EINA pin.                                                                                                                                    |  |  |  |

| Α             | EA    |                                                                                         | nput of EINA pin, EA bit is automatically cleared to zero to stop cting operation. To restart detection, resetting is needed.                                  |  |  |  |

|               |       |                                                                                         | tion flag is still remained. After input initial power,                                                                                                        |  |  |  |