# **Application Manual**

# Real Time Clock Module **RTC-7301SF/DG**

| Model      | Product Number   |

|------------|------------------|

| RTC-7301SF | QZ42730181000200 |

| RTC-7301DG | QZ42730111000200 |

EPSON TOYOCOM CORPORATION

# NOTICE

- The material is subject to change without notice.

- Any part of this material may not be reproduced or duplicated in any form or any means without the written permission of Epson Toyocom.

- The information, applied circuit, program, usage etc., written in this material is just for reference. Epson Toyocom does not assume any liability for the occurrence of infringing any patent or copyright of a third party. This material does not authorize the licensing for any patent or intellectual copyrights.

- Any product described in this material may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export licence from the Ministry of International Trade and industry or other approval from another government agency.

- You are requested not to use the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes. You are also requested that you would not make the products available to any third party who may use the products for such prohibited purposes.

- These products are intended for general use in electronic equipment. When using them in specific applications that require extremely high reliability such as applications stated below, it is required to obtain the permission from Epson Toyocom in advance.

- / Space equipment (artificial satellites, rockets, etc) / Transportation vehicles and related (automobiles, aircraft, trains, vessels, etc) / Medical instruments to sustain life / Submarine transmitters

- / Power stations and related / Fire work equipment and security equipment / traffic control equipment / and others requiring equivalent reliability.

- In this manual for Epson Tyocom, product code and marking will still remain as previously identified prior to the merger.Due to the on going strategy of gradual unification of part numbers, please review product code and marking as they will change during the course of the coming months. We apologize for the inconvenience, but we will eventually have a unified part numbering system for Epson Toyocom which will be user friendly.

# CONTENTS

| 1. Overview1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. Block diagram1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3. Terminal connections2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4. Terminal functions2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5. Characteristics       3         5-1. Absolute maximum ratings       3         5-2. Recommended operating conditions       3         5-3. Oscillating characteristics       3         5-4. DC characteristics       4         5-5. Pin capacity characteristics       5         5-6. Temperature sensor characteristics       6         5-7. AC characteristics       7                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6. Registers       8         6-1. Register table       8         6-2. Register description       9         6-2-1. Clock and calendar registers (Bank0, Reg-0 to Reg-E)       9         6-2-2. Alarm register (Bank1 Reg-0 to Reg-8 and Reg-E)       9         6-2-3. CS1 control registers (Bank1, Reg-B)       10         6-2-4. FOUT frequency setting registers (Bank1, Reg-C and D)       11         6-2-5. Timer register (Bank2, Reg-4 to Reg-8 and Reg-E)       11         6-2-6. Digital offset registers (Bank2 Reg-0, 1)       14         6-2-7. Control registers (Common to each Bank Reg-E and Reg-F)       15         6-2-8. Alarm interrupt       16         6-2-9. Timer interrupt       17         6-2-10. How to verify the digital offset       17         6-2-11. Timing of output signal.       18 |

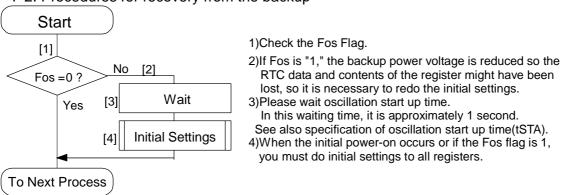

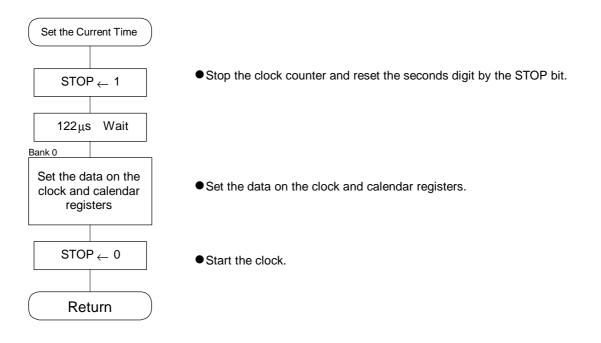

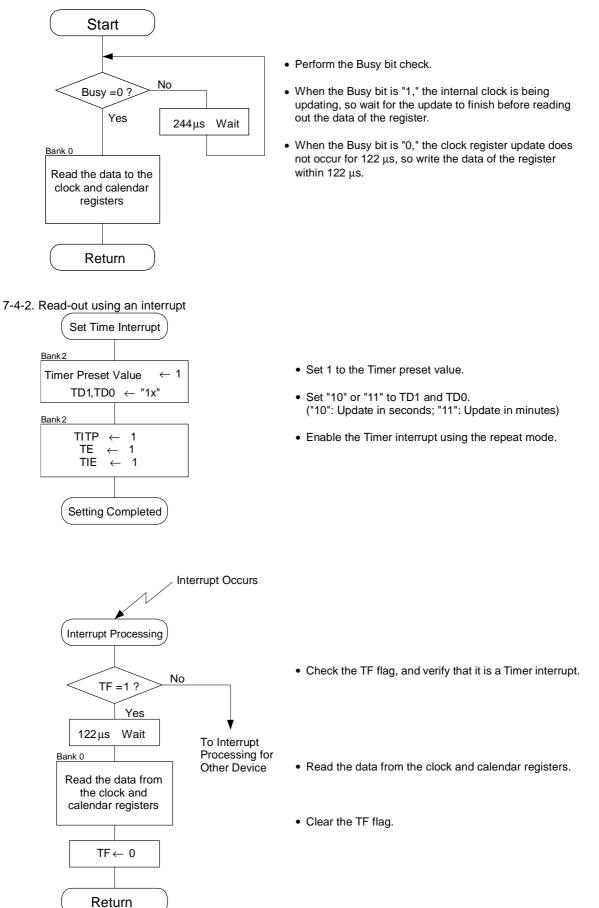

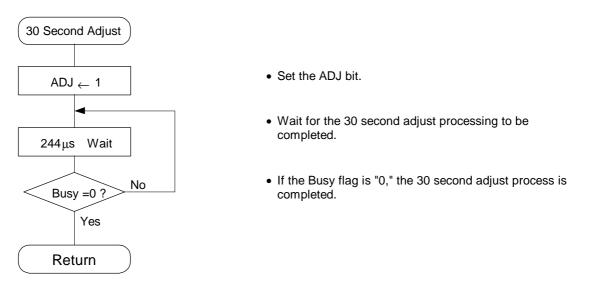

| 7. How to use       19         7-1. Procedures for initially turning ON the power <sup>*1</sup> (initial settings)       19         7-1-2. When used a digital pace adjustment function       20         7-2. Procedures for recovery from the backup       21         7-3. Writing to the clock and calendar (setting the current time)       21         7-4. Reading out the clock and calendar.       22         7-5. 30 second adjust <sup>*2</sup> 23                                                                                                                                                                                                                                                                                                                                                              |

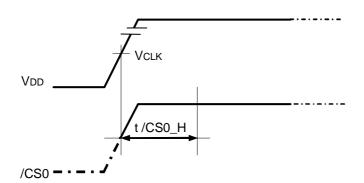

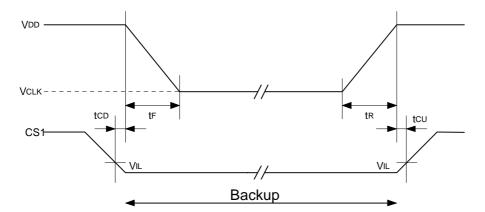

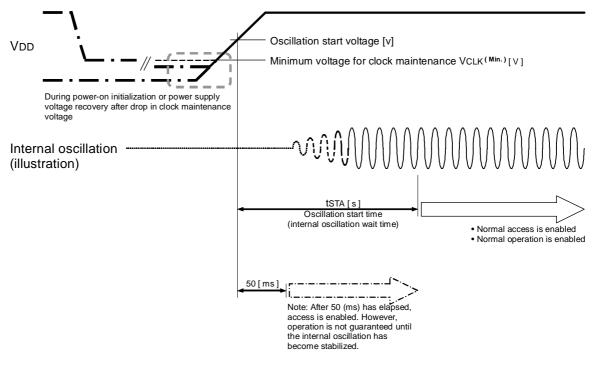

| 8. Matters that demand special attention on use       24         8.1. VDD and /CS0 timing       24         8.2. Shifting to backup and recovering       24         9.3. Restrictions on Access Operations During Power-on Initialization and Recovery from Backup 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

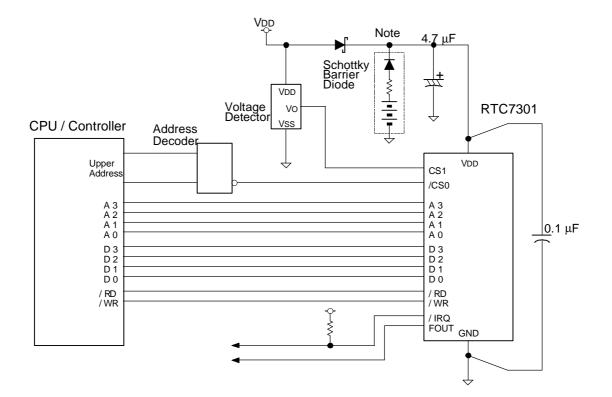

| 9. External connection example26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

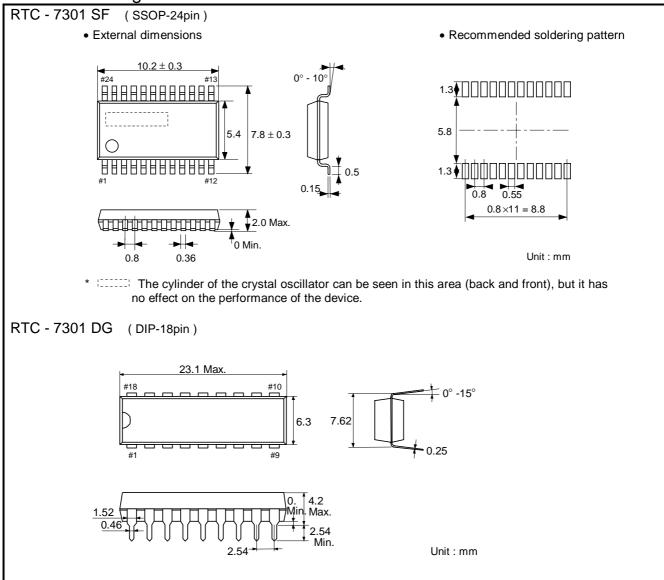

| 10. External diagram27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

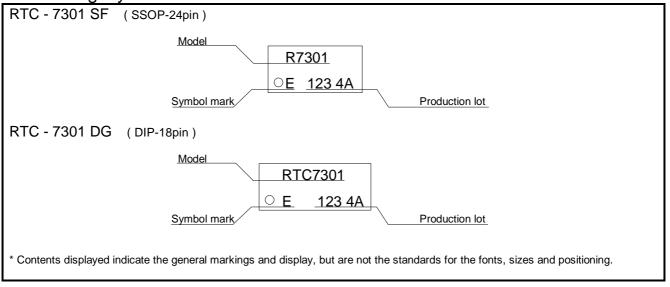

| 11. Marking layout27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

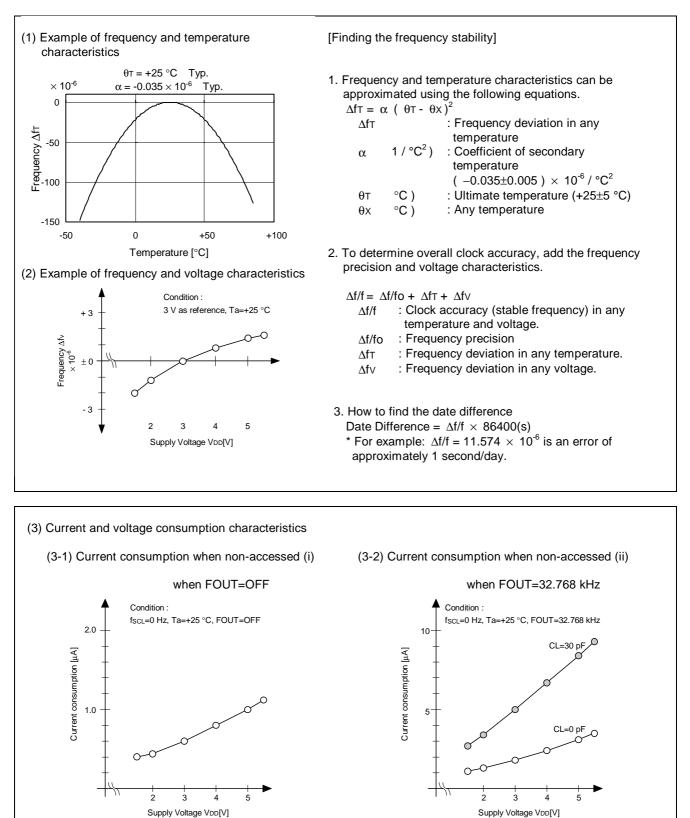

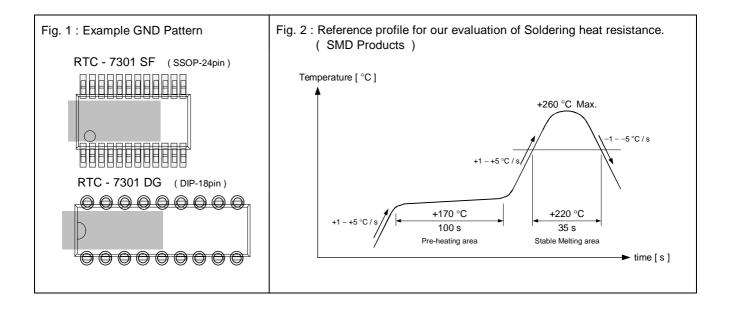

| 12. Reference data28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 13. Application notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Multi-function 4 bit Parallel RTC Module

# RTC - 7301 SF / DG

- Built-in crystal oscillator 32.768 kHz with frequency adjusted

- Frequency selectable clock output (  $32.768\ \text{kHz}$  to  $1/30\ \text{Hz}$  )

- Built-in 30 second adjustment function, digital pace adjustment function (max. adjustment:  $\pm$ 192  $\times$  10<sup>-6</sup>)

- Built-in alarm and timer interrupt functions

- Built-in semiconductor temperature sensor ( Voltage output: -7.8 mV / °C , RTC-7301SF )

- Operating voltage range: 2.4 V to 5.5 V, timekeeper (retained) voltage range: 1.6 V to 5.5 V

- Low current consumption (0.6 μA / 3V Typ.)

- High speed parallel interface compatible with S-RAM

# 1. Overview

This is a real-time clock module using a parallel interface method with a built-in crystal oscillator.

It has a variety of built-in functions such as the leap year Clock & Calendar circuit that automatically adjust from seconds to years, the alarm and timer interrupt functions, and the time update detector. It is also equipped with a frequency selectable clock output pin.

Furthermore, it has a digital pace adjustment function for adjusting the accuracy of the clock and a semiconductor temperature sensor (analog voltage output) to enable a more accurate clock system.

Also, the interface employed is a parallel interface that is compatible with S-RAM thereby making connections easier and high speed data communication possible.

We have both SSOP and DIP package types enabling this to be used on a wide range of electronic equipment such as computers, word processors, facsimiles, multi-function telephones, sequencers and various types of control equipment.

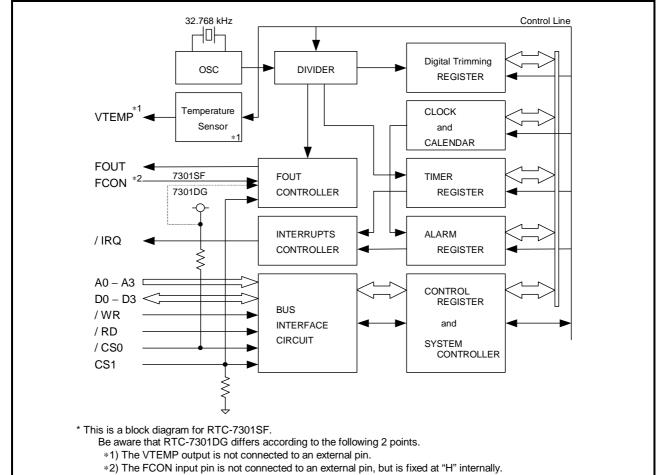

# 2. Block diagram

# 3. Terminal connections

| RTC - 7301 SF                                                                                                         | RTC - 7301 DG                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. / CS0<br>2. FCON<br>3. FOUT #1<br>4. VTEMP<br>5. (VDD)<br>6. / IRQ<br>7. A0<br>8. A1<br>9. A2<br>10. A3 #12<br>#13 | 24. VDD       1. / CS0       18. VDD         23. (VDD)       2. FOUT #1       #18 17. (VDD)         21. (VDD)       3. / IRQ       16. (VDD)         20. (VDD)       4. A0       15. CS1         19. (VDD)       5. A1       14. D0         16. D1       7. A3       12. D2         15. D2       8. / RD       #9       #10       11. D3         13. / WR       9. GND       10. / WR       10. / WR |

| SSOP - 24 pin                                                                                                         | DIP - 18 pin                                                                                                                                                                                                                                                                                                                                                                                         |

# 4. Terminal functions

| Pin      | Pin nu          | umber           |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|-----------------|-----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| name     | 7301SF<br>24pin | 7301DG<br>18pin | I/O    | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| /CS0     | 1               | 1               | Input  | This is a chip select 0 input pin and has a built-in pull-up resistor.<br>When /CS0="L",CS1="H," access of this device is possible.<br>Note: At the time of initial power-on, keep a level of CS 0 in High. Please use this device<br>after making CS0 a High level once after power-on when you cannot but start CS0 with a<br>Low level.                                                                                                                                  |

| FCON     | 2               | -               | Input  | This pin is only on the RTC7301SF. It selects the frequency to output to the FOUT pin.<br>This pin is fixed at 32.768 kHz output when FCON="L" and frequencies are selectable by<br>the FD bit when FCON="H."<br>Note: This pin is not found on RTC-7301DG. It is fixed at "H" internally.<br>Therefore, because FDOUT output frequencies are selected by the FD bit, set the FD bit and FE bit<br>to the appropriate setting when the frequency is output to the FOUT pin. |

| FOUT     | 3               | 2               | Output | This outputs the clock signal at the frequency set by the FD bit (CMOS output).<br>Furthermore, output is 32.768 kHz when FCON="L."<br>When there is no FOUT output, this pin is set to high impedance.                                                                                                                                                                                                                                                                     |

| VTEMP    | 4               | -               | Output | This is a temperature sensor output pin found only on RTC7301SF. (Analog voltage<br>output)<br>When there is no VTEMP output, this pin is set to high impedance.                                                                                                                                                                                                                                                                                                            |

| /IRQ     | 6               | 3               | Output | This is an N-ch open-drain interrupt output pin.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A0 to A3 | 7 to 10         | 4 to 7          | Input  | These are address input pins.<br>When accessing this device, this pin inputs the register address to select.                                                                                                                                                                                                                                                                                                                                                                |

| /RD      | 11              | 8               | Input  | This is a read strobe input pin.<br>Data can be read from RTC when /RD="L."                                                                                                                                                                                                                                                                                                                                                                                                 |

| GND      | 12              | 9               | -      | This pin is connected to the ground.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| /WR      | 13              | 10              | Input  | This is a write strobe input pin.<br>This pin writes data to the RTC at edge of the rise.                                                                                                                                                                                                                                                                                                                                                                                   |

| D0 to D3 | 14 to 17        | 11 to 14        | I/O    | These are data I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CS1      | 18              | 15              | Input  | This is a chip select 1 input pin and has a built-in pull-down resistor.<br>It is possible for the FOUT pin to output when CS1="H," regardless of the status of the<br>/CS0 pin.<br>The FOUT pin is set to high impedance when CS1="L."                                                                                                                                                                                                                                     |

| (VDD)    | 5, 19 - 23      |                 | -      | These pins have the same electrical potential as VDD, but, do not connect them to any external equipment.                                                                                                                                                                                                                                                                                                                                                                   |

| Vdd      | 24              | 18              | -      | Connect this to a + power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Note 1 ) Be sure to connect a filter capacity of at least  $0.1\mu$ F close to VDD - GND.

Note 2) When the /RD and /WR pins are both in the "L" state, mis-operations can occur. Avoid this state.

| <ul> <li>Relationship of FOLI</li> </ul> | T output and RTC access h | w the /CS0_CS' | 1 and FCON pins and the FE bit |

|------------------------------------------|---------------------------|----------------|--------------------------------|

|                                          |                           |                |                                |

| ······································ |     |      |    |                                    |              |  |  |

|----------------------------------------|-----|------|----|------------------------------------|--------------|--|--|

| / CS0                                  | CS1 | FCON | FE | FOUT output                        | RTC access   |  |  |

| L                                      | L   | Х    | Х  | High impedance                     | Not possible |  |  |

| Н                                      | Н   | L    | Х  | 32.768 kHz output                  | Not possible |  |  |

| Н                                      | Н   | Н    | 0  | High impedance                     | Not possible |  |  |

| Н                                      | Н   | Н    | 1  | FD bit selectable frequency output | Not possible |  |  |

| L                                      | Н   | L    | Х  | 32.768 kHz output                  | Possible     |  |  |

| L                                      | Н   | Н    | 0  | High impedance                     | Possible     |  |  |

| L                                      | Н   | Н    | 1  | FD bit selectable frequency output | Possible     |  |  |

# 5. Characteristics

# -1. Absolute maximum ratings

| -1. Absolute maximum ratings |        |                                     |                    |      |  |  |

|------------------------------|--------|-------------------------------------|--------------------|------|--|--|

| ltem                         | Symbol | Condition                           | Rated value        | Unit |  |  |

| Power supply voltage         | Vdd    | -                                   | -0.3 to +7.0       | V    |  |  |

| Input voltage                | Vin    | Input terminal, D0 to D3 pins       | GND-0.3 to Vdd+0.3 | V    |  |  |

| Output voltage (1)           | Vout1  | / IRQ pin                           | GND-0.3 to +8.0    | V    |  |  |

| Output voltage (2)           | Vout2  | FOUT, D0-D3 pins, VTEMP pin         | GND-0.3 to Vdd+0.3 | V    |  |  |

| Storage temperature          | Tstg   | Stored bare product after unpacking | -55 to +125        | °C   |  |  |

# -2. Recommended operating conditions

| -2. Recommended operating conditions |        |                 |            |      |  |

|--------------------------------------|--------|-----------------|------------|------|--|

| ltem                                 | Symbol | Condition       | Range      | Unit |  |

| Power supply voltage                 | Vdd    | -               | 2.4 to 5.5 | V    |  |

| Clock power supply voltage           | Vclk   | -               | 1.6 to 5.5 | V    |  |

| Operating<br>temperature             | Topr   | No condensation | -40 to +85 | °C   |  |

# -3. Oscillating characteristics

| ltem                                        | Symbol          | Condition                                                     | Rating                 | Unit                         |

|---------------------------------------------|-----------------|---------------------------------------------------------------|------------------------|------------------------------|

| Frequency precision                         | $\Delta$ f / fo | Ta= +25 °C, VDD=3.0 V                                         | 5 ± 23 <sup>(*1)</sup> | × 10 <sup>-6</sup>           |

| Frequency voltage characteristics           | f / V           | Ta= +25 °C, VDD=1.6 V to 5.5 V                                | ± 2 Max.               | × 10 <sup>-6</sup> / V       |

| Frequency<br>temperature<br>characteristics | Тор             | Ta= -10 °C to +70 °C, VDD=3.0 V<br>Ta=+25°C is standard (=0). | +10 / -120             | × 10 <sup>-6</sup>           |

| Oscillating starting time                   | <b>t</b> STA    | Ta= +25 °C, VDD=2.4 V                                         | 3 (Max.)               | S                            |

| Aging amount                                | fa              | Ta= +25 °C, VDD=3.0 V ; first year                            | ± 5 Max.               | imes 10 <sup>-6</sup> / year |

$^{\ast 1\,)}$  Equivalent to 1 minute of monthly deviation ( excluding offset ).

#### -4. DC characteristics

#### 5-4-1. DC characteristics (1)

Symbol Condition Min. Max. Unit Item Typ. /CS0,/RD,/WR=VDD, **I**DD1 VDD=5 V 1.0 2.0 μΑ Current consumption A0-A3, CS1=GND (When non-accessed) D0-D3,/IRQ=Hi-z, FOUT=Hi-FOUT =Output OFF z(OFF) VTEMP =Output OFF DD2 VDD=3 V 0.6 1.0 μΑ VTEMP=Hi-z(OFF) /CS0,/RD,/WR,CS1=VDD **I**DD3 VDD=5 V 3.0 7.5 μA A0-A3=GND, D0-D3, /IRQ=Hi-z FOUT=32 kHz Output, When CL= 0pF DD4 Vdd=3 V 1.7 4.5 μΑ Current consumption VTEMP=Hi-z(OFF) (When non-accessed) FOUT = 32 kHz Output /CS0,/RD,/WR,CS1=VDD VTEMP = Output OFF VDD=5 V DD5 8.0 20 μΑ A0-A3=GND D0-D3,/IRQ=Hi-z FOUT=32 kHz Output, When CL=30 pF VDD=3 V 5.0 12 1006 μΑ VTEMP=Hi-z(OFF) /CS0,/RD,/WR=VDD, IDD7 VDD=5 V 50 75 μΑ Ta= +25 °C Current consumption A0-A3,CS1=GND (When non-accessed) D0-D3,/IRQ=Hi-z FOUT = Output OFF FOUT=Hi-z(OFF) VDD=3 V **I**DD8 40 60 μΑ -VTEMP=ON

\* Unless specified otherwise : GND=0 V, VDD=1.6 V to 5.5 V, Ta= -40 °C to +85 °C

Note) There is no VTEMP pin on the RTC-7301DG so be aware of the following.

<sup>\*1</sup>) Does not apply for IDD7, IDD8.

<sup>\*2</sup>) Specifications for the VTEMP pin within the conditions described above do not apply for IDD1–IDD6.

-4-2. DC characteristics (2)

\* Unless specified otherwise : GND=0 V , VDD=1.6 V to 5.5 V , Ta= -40 °C to +85 °C

| ltem                  | Symbol |                              | Condition                                      | Min.    | Тур.    | Max.    | Unit |

|-----------------------|--------|------------------------------|------------------------------------------------|---------|---------|---------|------|

| Input voltage (1)     | VIH1   | VDD=4.5                      | /CS0, FCON, /RD, /WR                           | 2.2     |         | Vdd+0.3 | V    |

|                       | VIL1   | to 5.5 V                     | A0-A3, D0-D3 pins                              | GND-0.3 |         | 0.8     | V    |

|                       | VIH2   | VDD=2.4 /CS0, FCON, /RD, /WR | 0.8Vdd                                         |         | Vdd+0.3 | V       |      |

| Input voltage (2)     | VIL2   | v to 3.6 V                   | A0-A3, D0-D3 pins                              | GND-0.3 |         | 0.2Vdd  | V    |

| Input voltage (2)     | Vінз   | Vdd=1.6 V                    | 'DD=1.6 V                                      | 0.8Vdd  |         | Vdd+0.3 | V    |

| Input voltage (3)     | ViL3   | to 5.5 V                     | CS1 pin                                        | GND-0.3 |         | 0.2Vdd  | V    |

| Input leakage current | Ilek   |                              | DD, CS1:VIN=GND<br>/WR, A0-A3 : VIN=VDD or GND | -0.5    |         | 0.5     | μΑ   |

Note) There is no FCON pin on the RTC-7301DG so standards for the FCON pin within the conditions described above do not apply.

| Item                   | Symbol | ·                         | Condition                       | Min.  | Тур. | Max. | Unit |

|------------------------|--------|---------------------------|---------------------------------|-------|------|------|------|

| Pull-up resistor (1)   | RUP1   | Vdd=5 V                   | /CS0 pin                        | 75    | 150  | 300  | kΩ   |

| Pull-up resistor (2)   | Rup2   | Vdd=3 V                   | Vin=ĠND                         | 150   | 300  | 600  | kΩ   |

| Pull-down resistor (1) | Rdwn1  | Vdd=5 V                   | CS1 pin, VIN=VDD                | 20    | 40   | 80   | MΩ   |

| Pull-down resistor (2) | Rdwn2  | Vdd=3 V                   |                                 | 42.5  | 85   | 170  | MΩ   |

| Pull-down resistor (3) | Rdwn3  | Vdd=5 V                   | CS1 pin, Vıℕ=0.5 V              | 30    | 60   | 120  | kΩ   |

| Pull-down resistor (4) | Rdwn4  | Vdd=3 V                   | CS1 pin, Vıℕ=0.5 V              | 55    | 110  | 220  | kΩ   |

| "H" Output voltage (1) | Voh1   | Vdd=5 V                   | Іон= –1 mA                      | 4.5   |      | 5.0  | V    |

| "H" Output voltage (2) | Voh2   | Vdd=3 V                   | D0-D3, FOUT pin                 | 2.0   |      | 3.0  | V    |

| "H" Output voltage (3) | Vонз   | Vdd=3 V                   | Іон= –100 μА<br>D0-D3, FOUT pin | 2.9   |      | 3.0  | V    |

| "L" Output voltage (1) | Vol1   | Vdd=5 V                   | Iol= 1 mA                       | 0     |      | 0.5  | V    |

| "L" Output voltage (2) | Vol2   | Vdd=3 V                   | D0-D3, FOUT pin                 | 0     |      | 0.8  | V    |

| "L" Output voltage (3) | Vol3   | Vdd=3 V                   | IoL= 100 μA<br>D0-D3, FOUT pin  | 0     |      | 0.1  | V    |

| "L" Output voltage (4) | Vol4   | Vdd=5 V                   | lo∟= 1 mA                       | 0     |      | 0.25 | V    |

| "L" Output voltage (5) | Vol5   | Vdd=3 V                   | /IRQ pin                        | 0     |      | 0.4  | V    |

| Output leakage current | loz    | D0-D3, /IRQ<br>Vout=Vdd o |                                 | - 0.5 |      | 0.5  | μA   |

# -4-3. DC characteristics (3) Unless specified otherwise : GND=0 V, VDD=1.6 V to 5.5 V, Ta= -40 °C to +85 °C

# -5. Pin capacity characteristics

| Item                   | Symbol | Condition     | Min. | Тур. | Max. | Unit |

|------------------------|--------|---------------|------|------|------|------|

| Address input capacity | CADD   | A0 to A3 pins |      |      | 8    | pF   |

| Data input capacity    | Срата  | D0 to D3 pins |      |      | 15   | pF   |

|                                |        | GND=0 V, Vdd=                                                                 | :1.6 V to 5 | 5.5 V , Ta= | ⊨ –40  °C t | o +85 °C |

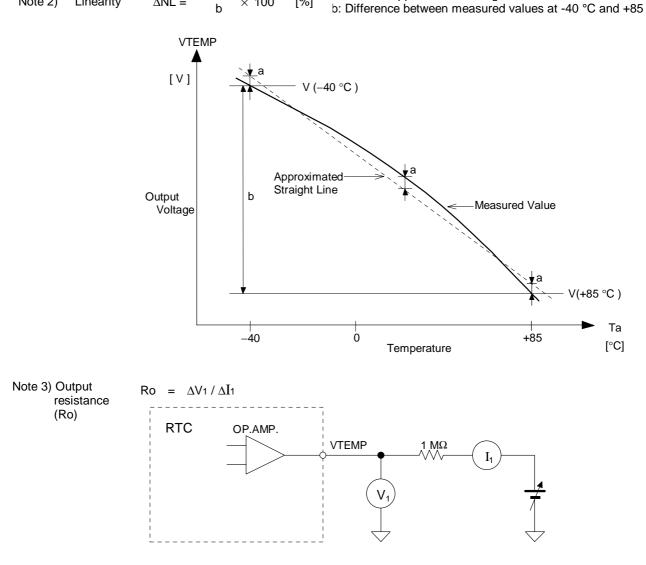

|--------------------------------|--------|-------------------------------------------------------------------------------|-------------|-------------|-------------|----------|

| ltem                           | Symbol | Condition                                                                     | Min.        | Тур.        | Max.        | Unit     |

| Temperature<br>output voltage  | VTEMP  | Ta= +25 °C , GND based output voltage<br>VTEMP pins, VDD=2.7 V to 5.5 V       |             | 1.470       |             | V        |

| Output precision               | TACR   | Ta =+25 °C , VDD=2.7 V to 5.5 V                                               |             |             | ± 5.0       | °C       |

| Temperature<br>sensitivity     | Vse    | –40 °C $\leq$ Ta $\leq$ +85 °C , VDD=2.7 V to 5.5V                            | -7.3        | -7.8        | -8.3        | mV/°C    |

| Linearity                      | ΔNL    | $-40~^\circ\text{C} \le \text{Ta} \le +85~^\circ\text{C}$ , VDD=2.7 V to 5.5V |             |             | ± 2.0       | %        |

| Temperature<br>detection range | TSOP   | $\Delta \text{NL} \leq \pm 2.0$ % , VDD=2.7 V to 5.5V                         | -40         |             | + 85        | °C       |

| Output resistance              | Ro     | Ta= +25 °C, VTEMP pins,<br>VDD=2.7 V to 5.5V<br>GND standard and VDD standard |             | 1.0         | 3.0         | kΩ       |

| Load condition                 | CL     | VDD=2.7 V to 5.5V                                                             |             |             | 100         | pF       |

|                                | RL     | VDD=2.7 V to 5.5V                                                             | 500         |             |             | kΩ       |

| Response time                  | tRSP   | Vdd=3.3 V CL=50 pF , RL=500 k $\Omega$ , Max. $\pm$ 1°C                       |             |             | 200         | μs       |

#### i-6. Temperature sensor characteristics

\* Unless specified otherwise : ~ •

Note1) Temperature VsE = ( V (+85 °C) – V ( -40 °C) ) / 125 [mV/°C] sensitivity

а

$\times$  100

[%]

Note 2) Linearity

$$\Delta NL =$$

a: Maximum deviation between the measure value of VTEMP and the approximated straight line. b: Difference between measured values at -40 °C and +85 °C

Note) There is no temperature sensor function on the RTC-7301DG.

# EPSON TOYOCOM

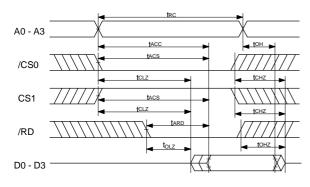

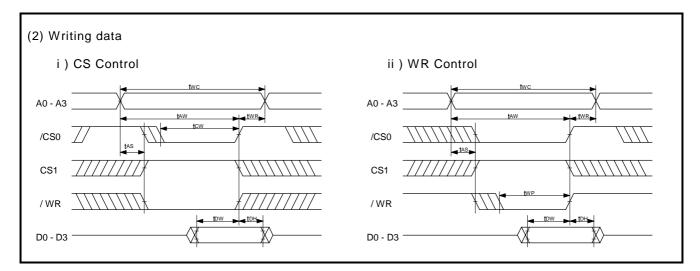

#### -7. AC characteristics

\* If not specifically  $\,$   $\bullet\,$  GND=0 V , Ta=  $-40\ ^\circ C$  to +85  $^\circ C$

indicated:

Input conditions: VI=0.5 × VDD, VO=0.5 × VDD

Output load: CL=100 pF (tacc.tacs.tard)

|                               |        | 1                    |                 | utput load: C |                 |      | RD)   |

|-------------------------------|--------|----------------------|-----------------|---------------|-----------------|------|-------|

| Item                          | Symbol | Condition            | VDD=2.4 to 3.6V |               | VDD=4.5 to 5.5V |      | Unit  |

|                               | Symbol | Condition            | Min.            | Max.          | Min.            | Max. | Offic |

| Read cycle time               | tRC    | -                    | 150             | -             | 85              | -    | Ns    |

| Address access time           | tACC   | -                    | -               | 150           | -               | 85   | Ns    |

| CE access time                | tacs   | -                    | -               | 150           | -               | 85   | Ns    |

| RD access time                | tard   | -                    | -               | 100           | -               | 45   | Ns    |

| CE output set time            | tcLz   | -                    | 5               | -             | 3               | -    | ns    |

| CE output floating            | tCHZ   | -                    | -               | 60            | -               | 30   | ns    |

| RD output set time            | tolz   | -                    | 5               | -             | 3               | -    | ns    |

| RD output floating            | tонz   | -                    | -               | 60            | -               | 30   | ns    |

| Output hold time              | tон    | -                    | 10              | -             | 5               | -    | ns    |

| Write cycle time              | twc    | -                    | 150             | -             | 85              | -    | ns    |

| Chip select time              | tcw    | -                    | 140             | -             | 70              | -    | ns    |

| Address valid to end of write | tAW    | -                    | 140             | -             | 70              | -    | ns    |

| Address setup time            | tAS    | -                    | 0               | -             | 0               | -    | ns    |

| Address hold time             | twr    | -                    | 0               | -             | 0               | -    | ns    |

| Write pulse width             | tWP    | -                    | 130             | -             | 65              | -    | ns    |

| Input data set time           | tDW    | -                    | 80              | -             | 35              | -    | ns    |

| Input data hold time          | tDH    | -                    | 0               | -             | 0               | -    | ns    |

| FOUT output frequency duty    | DUTY   | FOUT =<br>32.768 kHz | 40              | 60            | 40              | 60   | %     |

# (1) Reading data

# 6. Registers

# 6-1. Register table

Bank 0 Clock and calendar registers

| Address | Register            |    | bit 3               | bit 2               | bit 1 | bit 0               |

|---------|---------------------|----|---------------------|---------------------|-------|---------------------|

| 0       | 1 second            |    | 8                   | 4                   | 2     | 1                   |

| 1       | 10 second           |    | Fos                 | 40                  | 20    | 10                  |

| 2       | 1 minute            |    | 8                   | 4                   | 2     | 1                   |

| 3       | 10 minute           |    | 0                   | 40                  | 20    | 10                  |

| 4       | 1 hour              |    | 8                   | 4                   | 2     | 1                   |

| 5       | 10 hour             |    | 0                   | 0                   | 20    | 10                  |

| 6       | Day                 |    | 0                   | 4                   | 2     | 1                   |

| 7       | 1 day               |    | 8                   | 4                   | 2     | 1                   |

| 8       | 10 day              |    | 0                   | 0                   | 20    | 10                  |

| 9       | 1 month             |    | 8                   | 4                   | 2     | 1                   |

| Α       | 10 month            |    | 0                   | 0                   | 0     | 10                  |

| В       | 1 year              |    | 8                   | 4                   | 2     | 1                   |

| С       | 10 year             |    | 80                  | 40                  | 20    | 10                  |

| D       | 100 year            |    | 800                 | 400                 | 200   | 100                 |

| Е       | 1000 year           |    | *1,*2<br>TEST       | *1,*2<br>TEMP       | 2000  | 1000                |

| *1<br>F | Control<br>register | *1 | *1<br>Bank<br>Sel 1 | *1<br>Bank<br>Sel 0 | STOP  | *1<br>BUSY<br>/ ADJ |

#### Bank 2 Digital offset and timer registers

|         | 0                         |                     |                     | 0       |                     |

|---------|---------------------------|---------------------|---------------------|---------|---------------------|

| Address | Registers                 | bit 3               | Bit 2               | bit 1   | bit 0               |

| 0       | Digital offset            | DT3                 | DT2                 | DT1     | DT0                 |

| 1       | Digital Oliset            | DT_ON               | DT6                 | DT5     | DT4                 |

| 2       | _                         | 0                   | 0                   | 0       | 0                   |

| 3       | _                         | 0                   | 0                   | 0       | 0                   |

| 4       | Timer counter             | 8                   | 4                   | 2       | 1                   |

| 5       | preset value              | 128                 | 64                  | 32      | 16                  |

| 6       | Timer counter             | 8                   | 4                   | 2       | 1                   |

| 7       | data                      | 128                 | 64                  | 32      | 16                  |

| 8       | Timer settings            | TE                  | TI / TP             | TD1     | TD0                 |

| 9       | _                         | 0                   | 0                   | 0       | 0                   |

| А       | -                         | 0                   | 0                   | 0       | 0                   |

| В       | -                         | 0                   | 0                   | 0       | 0                   |

| С       | _                         | 0                   | 0                   | 0       | 0                   |

| D       | _                         | 0                   | 0                   | 0       | 0                   |

| Е       | Timer control             | *1,*2<br>TEST       | *1,*2<br>TEMP       | TF      | TIE                 |

| *1<br>F | *1<br>Control<br>register | *1<br>Bank<br>Sel 1 | *1<br>Bank<br>Sel 0 | STOP *1 | *1<br>BUSY<br>/ ADJ |

#### Bank 1 Alarms and FOUT registers

| Address | Register                                  | bit 3               | bit 2               | bit 1   | bit 0               |

|---------|-------------------------------------------|---------------------|---------------------|---------|---------------------|

| 0       | 1 second                                  | 8                   | 4                   | 2       | 1                   |

| 1       | 10 second                                 | AE                  | 40                  | 20      | 10                  |

| 2       | 1 minute                                  | 8                   | 4                   | 2       | 1                   |

| 3       | 10 minute                                 | AE                  | 40                  | 20      | 10                  |

| 4       | 1 hour                                    | 8                   | 4                   | 2       | 1                   |

| 5       | 10 hour                                   | AE                  | •                   | 20      | 10                  |

| 6       | Day                                       | AE                  | 4                   | 2       | 1                   |

| 7       | 1 day                                     | 8                   | 4                   | 2       | 1                   |

| 8       | 10 day                                    | AE                  | •                   | 20      | 10                  |

| 9       | -                                         | •                   | •                   | •       | •                   |

| Α       | -                                         | ٠                   | •                   | •       | •                   |

| В       | CS1<br>Controller                         | CTEMP               | CDT_ON              | •       | •                   |

| С       | FOUT divider<br>ratio setting<br>register | 0                   | FD2                 | FD1     | FD0                 |

| D       | FOUT divider<br>ratio setting<br>register | FE                  | ο                   | FD4     | FD3                 |

| Е       | Alarm control                             | *1,*2<br>TEST       | *1,*2<br>TEMP       | AF      | AIE                 |

| *1<br>F | *1<br>Control<br>register                 | *1<br>Bank<br>Sel 1 | *1<br>Bank<br>Sel 0 | STOP *1 | *1<br>BUSY<br>/ ADJ |

1) [\*1] bits (all bits of the control registers and the TEST bits and TEMP bits) are common for all BANKs.

2) When the power is turned on initially, the [\*2] TEST and TEMP bits are cleared to 0. Also, Fos is set to 1, but because other the register values of other bits are unknown, always make their initial settings. When doing so, do not make settings for date and time that are impossible. We do not guarantee proper operation of the clock for such settings. When digital pace adjustment function is not used , please clear a DT\_ON bit to 0 at the time of initial setting, by all means.

3) The TEST bit is our internal test bit.

Always use with this set to "0." Note) When using the RTC-7301DG, always use with the [\*2] TEST and TEMP bits set to "0."

- 4) Write is possible for the AF and TF bits only when set to "0."

- 5) "  $\circ$  " bits should be used when set to "0" after the initial settings.

- 6) " " bits can be used as RAM.

7) When not using the alarm interrupt, it is possible to use BANK 1 registers 0 to 8 as RAM. (Total 36 bits)

- 8) When not using the timer interrupt, it is possible to use BANK 2 registers 4 to 5 as RAM. (Total 8 bits)

- 9) When not using digital pace adjustment, Bank 2 registers 0 to 1 can be used as RAM except DT\_ON. (Total 7 bits)

- 10) The BUSY/ADJ bit is busy when reading and is a 30 second ADJ bit when writing. Also, a BUSY flag is set 122  $\mu$ s before and after the time update timing. The ADJ bit is cleared to 0 automatically at a maximum of 244  $\mu$  s after being set.

#### 6-2. Register description

6-2-1. Clock and calendar registers (Bank0, Reg-0 to Reg-E)

- Data is in BCD format. For example, if the 10 second register is "0101" and the 1 second register is "1001" it has the meaning of 59 seconds.

- The clock keeps time using a 24 hour format.

- Leap years are automatically determined between the years of 1901 and 2099.

- Days are in Bank 0 Reg-6.

- Day registers are in 3 bits from bit 0 to 2 and are allocated as shown in the following table.

| Bit 2 | bit 1 | bit 0 | Day    |

|-------|-------|-------|--------|

| 0     | 0     | 0     | Sun.   |

| 0     | 0     | 1     | Mon.   |

| 0     | 1     | 0     | Tues.  |

| 0     | 1     | 1     | Wed.   |

| 1     | 0     | 0     | Thurs. |

| 1     | 0     | 1     | Fri.   |

| 1     | 1     | 0     | Sat.   |

• Fos (Oscillation voltage decrease detection bit)

This flag is a bit for recording the decrease in voltage on the crystal oscillator. It detects the decrease in the voltage of the crystal oscillator that is in use and is a flag bit for notifying the decrease in the reliability of the time data. "1" indicates a decrease in the voltage and it is retained until a "0" is written.

This is not affected by the function of other bits.

6-2-2. Alarm register (Bank1 Reg-0 to Reg-8 and Reg-E)

• AE bit: (Alarm Enable)

This bit enables the setting of the alarms for date, day, hour, minute and second.

An AE bit accompanies the alarm register, so using this bit makes it easy to set the alarm for each second, each minute, each hour, each day or each date.

It is not possible to set a multiple of days at one time.

When the AE bit is 0, the appropriate register and the clock register are compared; when the bit is 1, this means "don't care" and the data is ignored and the two are regarded as the same.

• Example of setting day alarm bits for each day (Bank1 Reg-6)

| bit 2 | bit 1 | bit 0 | Day    |

|-------|-------|-------|--------|

| 0     | 0     | 0     | Sun.   |

| 0     | 0     | 1     | Mon.   |

| 0     | 1     | 0     | Tues.  |

| 0     | 1     | 1     | Wed.   |

| 1     | 0     | 0     | Thurs. |

| 1     | 0     | 1     | Fri.   |

| 1     | 1     | 0     | Sat.   |

• AF bit: (Alarm Flag)

The AF bit is "1" when an alarm occurs.

This data is retained until a "0" is written. It is not possible to write "1."

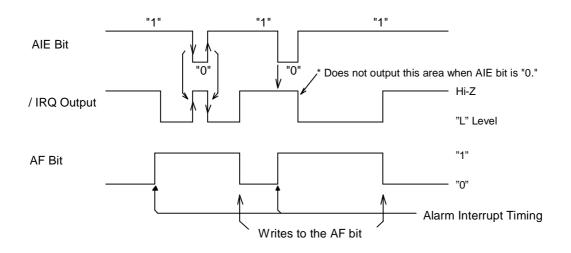

• AIE bit: ( Alarm Interrupt Enable )

This bit sets whether or not to output the alarm interrupt signal to the /IRQ pin.

The /IRQ pin is Low active when the AF bit is set to 1 at the time of an alarm interrupt, if the AIE bit is "1." An alarm interrupt output is prohibited from the /IRQ pin when the AIE bit is "0." It is necessary to set the AIE bit to "1" in order to have an alarm interrupt

It is necessary to set the AIE bit to "1" in order to have an alarm interrupt.

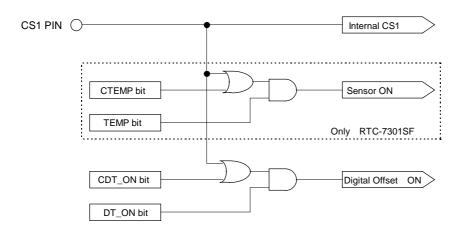

6-2-3. CS1 control registers (Bank1, Reg-B)

| Address | Register    | bit 3 | bit 2  | bit 1 | bit 0 |

|---------|-------------|-------|--------|-------|-------|

| В       | CS1 control | CTEMP | CDT_ON | ٠     | •     |

The CS 1 control register CTEMP bit selects whether or not to link the temperature sensor operation with the logic status of each CS1 pin. The CDT\_ON bit selects whether or not to link the digital pace adjustment function (called digital offset below) with the logic status of each CS1 pin.

#### •CTEMP bit

Setting CTEMP to "0" will operate the temperature sensor only when the CS1 pin is "H."

Setting CTEMP to "1" will operate the temperature sensor regardless of the CS1 pin.

(A separate TEMP bit setting is necessary for the operation of the temperature sensor.)

Note) Set to [CTEMP bit = "0"] because there is no temperature sensor output for the RTC-7301DG.

#### •CDT\_ON bit

Setting CDT\_ON to "0" will operate the digital offset only when the CS1 pin is "H." Setting CDT\_ON to "1" will operate the digital offset regardless of the CS1 pin. (A separate DT\_ON bit setting is necessary for the operation of the digital offset.)

#### •Function operating tables

1) Temperature sensor

| CS1 Pin | CTEMP bit | TEMP bit | Temperature sensor |

|---------|-----------|----------|--------------------|

| Х       | Х         | 0        | Stops              |

| L       | 0         | 1        | Stops              |

| Н       | 0         | 1        | Runs               |

| L       | 1         | 1        | Runs               |

| Н       | 1         | 1        | Runs               |

Note) This function does not operate because there is no temperature sensor function on the RTC-7301DG.

#### 2) Digital offset

| CS1 Pin | CDT_ON bit | DT_ON bit | Digital offset |

|---------|------------|-----------|----------------|

| Х       | Х          | 0         | Stops          |

| L       | 0          | 1         | Stops          |

| Н       | 0          | 1         | Runs           |

| L       | 1          | 1         | Runs           |

| Н       | 1          | 1         | Runs           |

6-2-4. FOUT frequency setting registers ( Bank1, Reg-C and D )

| Address | Registers                     | bit 3 | bit 2 | Bit 1 | bit 0 |

|---------|-------------------------------|-------|-------|-------|-------|

| С       | FOUT divider ratio<br>setting | 0     | FD2   | FD1   | FD0   |

| D       | FOUT frequency<br>setting     | FE    | 0     | FD4   | FD3   |

• FE bit: (Fout Enable)

When the FCON bit is "H," the specified frequency (source clock) is output from the FOUT pin at the specified divider ratio when the FE bit is "1."

When the FE bit is "0," output enters a prohibitive state (high impedance).

When the FCON pin is "L," 32.768 kHz is output from the FOUT pin regardless of the content of the Reg-C and D. Note) Internally, [FCON pin = "H"] on the RTC-7301DG.

• FD bit

| FD4 | FD3 | Source clock |

|-----|-----|--------------|

| 0   | 0   | 32768 Hz     |

| 0   | 1   | 1024 Hz      |

| 1   | 0   | 32 Hz        |

| 1   | 1   | 1 Hz         |

| FD2 | FD1 | FD0 | Divider ratio | FOUT duty |

|-----|-----|-----|---------------|-----------|

| 0   | 0   | 0   | 1/1           | 1/2       |

| 0   | 0   | 1   | 1/2           | 1/2       |

| 0   | 1   | 0   | 1/3           | 1/3       |

| 0   | 1   | 1   | 1/6           | 1 / 2     |

| 1   | 0   | 0   | 1/5           | 1 / 5     |

| 1   | 0   | 1   | 1 /10         | 1/2       |

| 1   | 1   | 0   | 1 /15         | 1/3       |

| 1   | 1   | 1   | 1 /30         | 1 / 2     |

6-2-5. Timer register (Bank2, Reg-4 to Reg-8 and Reg-E)

These registers control the 8 bit pre-settable down-counter used in the timer interrupt. The down-counter counting cycle (source clock) is specified by Reg-8 TD0 and TD1. Reg-4 and 5 specify the preset (divider) value of the down-counter.

The down-counter continues counting down using the specified source clock period. When it reaches zero, the TF (Timer Flag) is set to "1."

At this time, when the Reg-E TIE (Timer Interrupt Enable) bit is "1," the /IRQ pin becomes a Low level and an interrupt occurs. When the TIE bit is "0," output from the /IRQ pin is prohibited. Also, when the TI / TP bits are "1," the timer counter register data is re-loaded and another count-down is started. (Repeat operation)

| TD1 | TD0 | Source clock | IRQ automatic return time |  |  |  |

|-----|-----|--------------|---------------------------|--|--|--|

| 0   | 0   | 4096 Hz      | 0.122 ms                  |  |  |  |

| 0   | 1   | 64 Hz        | 7.81 ms                   |  |  |  |

| 1   | 0   | Update in    | 7.81 ms                   |  |  |  |

|     | •   | seconds      |                           |  |  |  |

| 1   | 1   | Update in    | 7.81 ms                   |  |  |  |

| I   | I   | minutes      |                           |  |  |  |

#### • Timer interrupt source clock selections

#### Timer interrupt intervals

| Timer counter  | Source clock |           |                      |                      |  |  |

|----------------|--------------|-----------|----------------------|----------------------|--|--|

| setting values | 4096 Hz      | 64 Hz     | Update in<br>seconds | Update in<br>minutes |  |  |

| 0              | -            | -         | -                    | -                    |  |  |

| 1              | 244.14 μs    | 15.625 ms | 1 s                  | 1 min                |  |  |

| 2              | 488.28 μs    | 31.250 ms | 2 s                  | 2 min                |  |  |

| 3              | 732.42 μs    | 46.875 ms | 3 s                  | 3 min                |  |  |

| •              | ٠            | •         | •                    | •                    |  |  |

| •              | •            | •         | •                    | •                    |  |  |

| •              |              |           | •                    | •                    |  |  |

| 255            | 62.26 ms     | 3.984 s   | 255 s                | 255 min              |  |  |

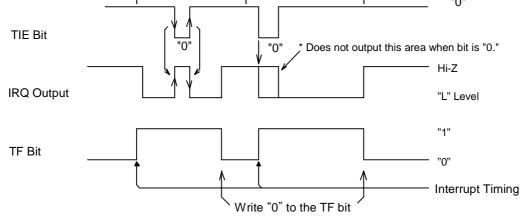

- TF bit: (Timer Flag) The TF bit set to 1 when the timer reaches zero. The data is maintained until 0 is written. It is not possible to write 1.

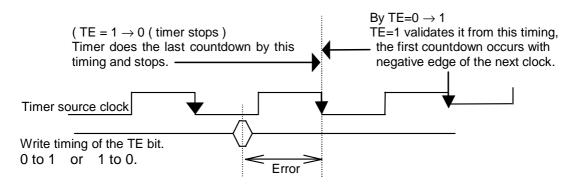

- TE bit: (Timer Enable) When TE is set to 1, timer is running. When TE is cleared to 0, Timer stops.

- TIE bit: ( Timer Interrupt Enable )

This bit determines whether or not to drive the /IRQ pin when there has been a timer interrupt. When the TIE bit is "0," the timer interrupt is not output to the /IRQ pin.

• TI/TP bits: (Interrupt Signal Output Mode Select. Interrupt / Periodic ) These bits set the output mode of the timer interrupt signal.

| TI/TP    | 0                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                    |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function | • Level interrupt mode<br>The /IRQ pin is "L" immediately upon the<br>occurrence of the timer interrupt (however,<br>when TIE = 1) and the TF bit is "1" and the<br>/IRQ is maintained at "L" until "0" is written<br>to the TF bit. | • Repeat interrupt mode (interval)<br>The /IRQ pin is "L" immediately upon the<br>occurrence of the timer interrupt (however, when<br>TIE = 1) and the TF bit is "1."<br>Subsequently, the /IRQ pin enters high impedance<br>and the TF bit is "1" is retained until "0" is written. |

- Alarm-interrupt and a both signal of a timer-interrupt output it from /IRQ terminal.

- Even if the output of one interrupt is prohibition state, another interrupt occur and /IRQ terminal becomes LOW active if it is a state of the output permission.

- If the hardware interrupt is not being used, clear both the TIE and AIE bits to "0" and monitor both flag bits of AF and TF with the software, if necessary.

- Timer operation when the TI/TP bit is "0" is that the timer count register counts down and when the data reaches zero, the TE bit is cleared and the counter automatically stops. The value of the timer count register when the timer automatically stops is zero.

- Timer operation when the TI/TP bit is "1" is that the timer counter register counts down and when the data reaches zero, the timer counter register data is reloaded and count down begins again. This can be used as the interval timer (repeat mode).

- Reg-6 and 7 are read only, and can read the current value of the 8 bit pre-settable down counter. It cannot write the data.

- The pre-settable binary down-counter is updated when data is written to the Reg-4 and 5 registers. Data written to the Reg-4 and 5 registers is retained until it is written again.

- A timer interrupt does not occur from the /IRQ pin even if the data when the timer counter (Reg-4 and 5) reaches zero is set when the TE bit is "1."

- There is an error in time of 0 to -1 cycles of the selected source clock with 1 timer operation.

- Also, if the timer operation time is less than 1 cycle of the source clock, the count will may not be performed normally.

- Particularly, be aware that, when using minute update clock from clock register, for the source clock, there will be an error of a maximum of 60 seconds depending on the timing.

- The timer starts counting down from the edge of the rise of /WR corresponding to the TE bit in the time chart below, in the data write mode.

- When the TE bit is "0," the counter stops. When the TE bit is "1", the count starts.

- Using this function enables you to stop the counter part-way through timer operations, but when the timer starts, be aware that an error will occur at the maximum of the source clock period.

- For example, when source clock set to 1 minute. Timer does countdown and stops from TE=0 after 1 minute (maximum), and there is the case that interrupt occurs.

- When interrupt is unnecessary, set TIE bits adequately, and prohibit unprepared interrupt.

6-2-6. Digital offset registers (Bank2 Reg-0,1)

| Address | Registers      | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|----------------|-------|-------|-------|-------|

| 0       | Digital Offset | DT3   | DT2   | DT1   | DT0   |

| 1       |                | DT_ON | DT6   | DT5   | DT4   |

• When DT\_ON="1", the digital pace adjustment function is enabled. When pace adjustment is enabled, the digital offset register digitally offsets the timekeeper according to the values set for the digital offset register by changing one second of the clock count every 10 seconds.

Linking the digital pace adjustment operation with the status of the CS 1 pin will set the CDT\_ON bit (Bank1,RegB)= "1".

When disabled digital pace adjustment, set to DT\_ON= "0."

[When a digital pace adjustment function is not used.]

At the time of initial setting, please clear a DT\_ON bit to 0 by all means.

[When used a digital pace adjustment function.]

When it is used a digital pace adjustment function, please perform an initialization in a specified procedure in initial power on by all means.

Please set it according to a procedure of 7-1-2 "When used a digital pace adjustment function." of "7-1 Procedures for initially turning ON the power"

• The relationship between offset range and resolution

| Offset range                                         | Offset resolution     | Offset timing       |

|------------------------------------------------------|-----------------------|---------------------|

| $-195.20 \times 10^{-6}$ to $+192.15 \times 10^{-6}$ | $3.05 \times 10^{-6}$ | Every 10<br>seconds |

The offset range is prescribed using frequency.

#### • The relationship of the DT bit and the digital offset value

When the DT6 bit = "0", it is a positive offset, when the DT6 bit = "1", it is a negative offset.

|     | Offset value |     |     |     |         |   |                     |  |

|-----|--------------|-----|-----|-----|---------|---|---------------------|--|

| DT6 | DT5          | DT4 | DT3 | DT2 | DT1 DT0 |   | $( \times 10^{-6})$ |  |

| 0   | 1            | 1   | 1   | 1   | 1       | 1 | +192.15             |  |

| 0   | 1            | 1   | 1   | 1   | 1       | 0 | +189.10             |  |

|     |              |     |     |     |         |   |                     |  |

| 0   | 0            | 0   | 0   | 0   | 1       | 0 | +6.10               |  |

| 0   | 0            | 0   | 0   | 0   | 0       | 1 | +3.05               |  |

| 0   | 0            | 0   | 0   | 0   | 0       | 0 | ±0.00               |  |

| 1   | 1            | 1   | 1   | 1   | 1       | 1 | -3.05               |  |

| 1   | 1            | 1   | 1   | 1   | 1       | 0 | -6.10               |  |

|     |              |     |     |     |         |   | •                   |  |

| 1   | 0            | 0   | 0   | 0   | 0       | 1 | -192.15             |  |

| 1   | 0            | 0   | 0   | 0   | 0       | 0 | -195.20             |  |

The offset value is shift value for internal real crystal frequency.

• How to calculate the offset value

1) When the offset value is positive:

DT [6 to 0] = [ Offset Value ] / 3.05

However, decimals are discarded.

Example Calculation: When the offset value is  $+192.15 \times 10^{-6}$ DT[6 to 0] = 192.15 / 3.05 = 63 (dec) = 0111111(bin) is set.

2) When the offset value is negative: DT[6 to 0] = 128 - [ Offset Value ]/ 3.05

However, decimals are discarded.

Example Calculation: When the offset value is  $-158.6 \times 10^{-6}$ DT[6 to 0] = 128 - (158.6 / 3.05) = 76(dec) = 1001100(bin) is set. 6-2-7. Control registers (Common to each Bank Reg-E and Reg-F )

| Address | bit 3      | Bit 2      | bit 1 | bit 0    |

|---------|------------|------------|-------|----------|

| E       | TEST       | TEMP       |       |          |

| F       | Bank Sel 1 | Bank Sel 0 | STOP  | BUSY/ADJ |

#### • TEST bit: This bit is for our internal testing.

Note) The TEST bit is for our internal testing, so always set to [ TEST bit - "0" ].

Be careful not to mistakenly write a "1" when writing data to other bits of the same register.

#### • TEMP bit

When this bit is set to "1", the VTEMP pin outputs the temperature sensor voltage (analog).

When it is set to "0," the VTEMP pin is set to a high impedance. This bit is reset to "0" when the power is turned ON.

Note) Because the VTEMP pin is not set on the RTC-7301DG, always set to [ TEMP bit = "0" ]. When using with [ TEMP bit = "1" ], power current consumption will increase.

#### Bank Sel bit

This bit specifies the Bank to access (read/write)

| Bank Sel 1 | Bank Sel 0 | Access bank name |

|------------|------------|------------------|

| 0          | 0          | Bank0            |

| 0          | 1          | Bank1            |

| 1          | 0          | Bank2            |

| 1          | 1          | Bank1            |

#### STOP bit

When this bit is set to "1", the timekeeper is set to STOP and RESET from the 32 Hz divider counter. This is used when setting the clock data.

The timekeeper starts when it is "0."

When setting the date and time data, wait a minimum of 122  $\mu s$  after writing "1" to this bit, then set the date and time data.

#### BUSY/ADJ bit

This bit is in BUSY mode when reading and in ADJ mode when writing. The data"1" can't set to this bit. When "1" is written to this bit, the following operations will be performed between a minimum of 61  $\mu$ s to a maximum of 183  $\mu$ s.

- When the seconds display is 00 to 29 Resets the counter up to 32 Hz for the seconds and sets the second digits to 00 seconds.

- When the seconds display is 30 to 59 ——Resets the counter up to 32 Hz for the seconds and sets the second digits to 00 seconds and adds one minute to the minute digit. Later, this bit is automatically reset to "0" after 244 μs (Max.)

Because when BUSY = 1, the counter is updated, read out to the clock and calendar when BUSY = 1. If BUSY=0, it reads out stable data without updating the time at a maximum of 122  $\mu$ s.

There is a possibility that unstable data will be read out while updating the clock if reading out when BUSY=1. The following will occur when BUSY=1.

- 1) Normal 1 second digit raise is processed.

- 2) Processing of the  $\pm 30$  second adjust (When writing 1 to the ADJ bit.)

#### • Function operation table

| B    | bit |                  | Fun                |       |                    |

|------|-----|------------------|--------------------|-------|--------------------|

| STOP | ADJ | Clock            | Timer              | Alarm | FOUT               |

| 0    | 0   | Runs             | Runs <sup>*1</sup> | Runs  | Runs <sup>*1</sup> |

| 0    | 1   | 30 adjust.       | Runs <sup>*1</sup> | Runs  | Runs <sup>*1</sup> |

| 1    | 0   | Stops            | *1                 | Stops | *2                 |

| 1    | 1   | Stops&30 adjust. | *1                 | Stops | *2                 |

\*1: When source clock set to 1Hz or 1 minute, in a timing of digital adjustment or 30ADJ, a period of a timer and a period of FOUT change a little. When STOP-Bit is "1", operation is stops.

\*2 : When source clock is 1Hz, The output is halt.

6-2-8. Alarm interrupt

- The /IRQ pin becomes "L" output when AIE = 1 when the alarm is matched, and it becomes high impedance when AIE = 0.

- An alarm interrupt is output when a carry occurs in the seconds digit.

6-2-8-1. How to use the alarm

Alarms can be set for dates, days, hours, minutes and seconds. It is not possible to set a multiple of days at one time.

In order to avoid careless hardware interrupts while setting the alarms, we recommend setting both the AF and AIE bits to "0" first. Then, set the alarm data and clear the AF flag to zero once to ensure its initialization. When finished, set the AIE bit to "1". If you do not wish to use the hardware interrupt, set the AIE bit to "0" and monitor the AF bit with the software as is necessary.

#### 6-2-8-2. Example of use

- 1) Issuing an alarm at 6:00 PM the next day:

- Write "0" to the AIE bit, and "0" to the AF bit.

- Write "1" to the AE bit of the date alarm.

- Acquire the current date in the Bank 0 register 6 to the day alarm register and write the next day's data in the day setting table. (If the acquired data is 6/H (Saturday), write 0/H (Sunday).)

- Write "18h" to the hour alarm register.

- Write "00h" to the minute alarm register.

- Write "00h" to the second alarm register.

- Clear the AF bit to zero.

- Write "1" to the AIE bit.

- 2) Issuing an alarm at 6:00 AM every Sunday morning:

- Write "0" to the AIE bit, and "0" to the AF bit.

- Write "1" to the AE bit of the date alarm.

- Write "0h" to the day alarm register.

- Write "06h" to the hour alarm register.

- Write "00h" to the minute alarm register.

- Write "00h" to the second alarm register.

- Clear the AF bit to zero.

- Write "1" to the AIE bit.

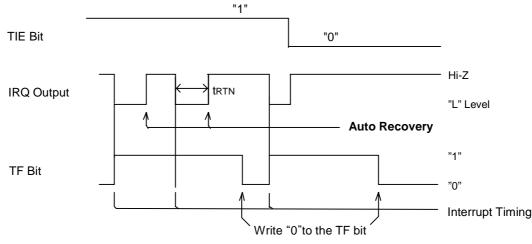

#### 6-2-9. Timer interrupt

- Setting the TI / TP bit enables selection of the level interrupt or the repeat interrupt modes.

- (1) Level interrupt mode (TI / TP = "0") When an interrupt occurs, and TIE =1, the /IRQ pin outputs "L" and if TIE = 0, the /IRQ pin becomes high impedance.

"1"

"1"

"0"

(2) Repeat mode (TI/TP = "1")

When an interrupt occurs, and TIE = 1, the /IRQ pin outputs "L."

When an interrupt occurs and TIE = 0, only the TF bit is "1" while the /IRQ pin stays at high impedance. This state is retained.

\*Auto recovery time of the interrupt output in the repeat mode The auto recovery time (tRTN) is different by the source clock specified by Bank1 Reg-D (FD3 and FD4 bits).

| Relationship | of pack | SOURCO   | clock and | auto | recovery | timpe |

|--------------|---------|----------|-----------|------|----------|-------|

| Relationship | 01 6461 | 1 300100 | CIOCK and | auto | recovery | unico |

| Source clock | Auto recovery times (tRTN) |  |  |  |

|--------------|----------------------------|--|--|--|

| 4069 Hz      | 0.122 ms                   |  |  |  |

| 64 Hz        | 7.81 ms                    |  |  |  |

| Update in    | 7.81 ms                    |  |  |  |

| seconds      | 7.61 113                   |  |  |  |

| Update in    | 7.81 ms                    |  |  |  |

| minutes      | 7.01 1115                  |  |  |  |

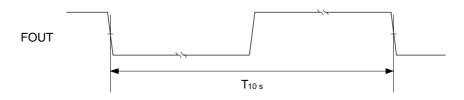

6-2-10. How to verify the digital offset

Because the digital offset is performed every 10 seconds, the results of the digital offset outputs a 10 s signal from the FOUT pin and this allows monitoring.

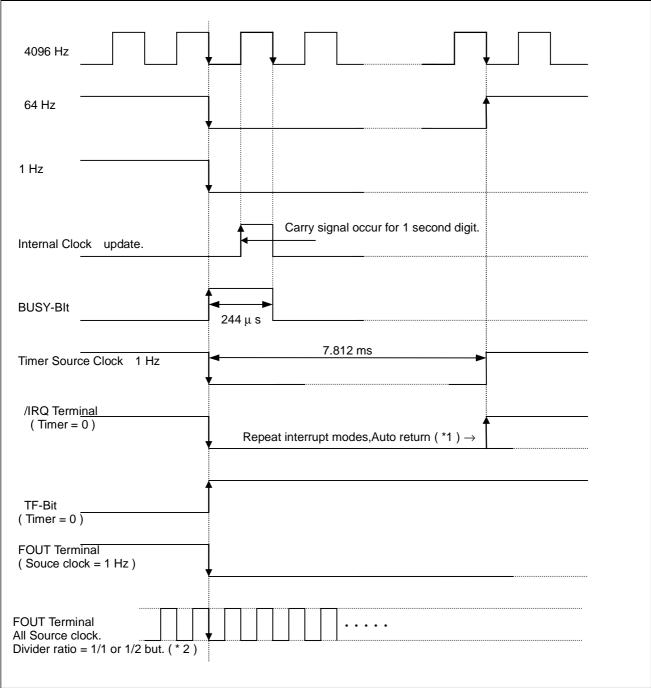

6-2-11. Timing of output signal.

The following charts are the timing of output signal of FOUT, Timer, Clock update and Flag-bit.

\*1 When source clock is 4096 Hz, automatic return with 122  $\mu s.$

\*2 FOUT is asynchronous to edge of 1Hz, when source-clock is 32768 Hz, 1024 Hz, 32 Hz (excludes 1 Hz), and Divider ratio set 1/3 or 1/5 only.

# 7. How to use

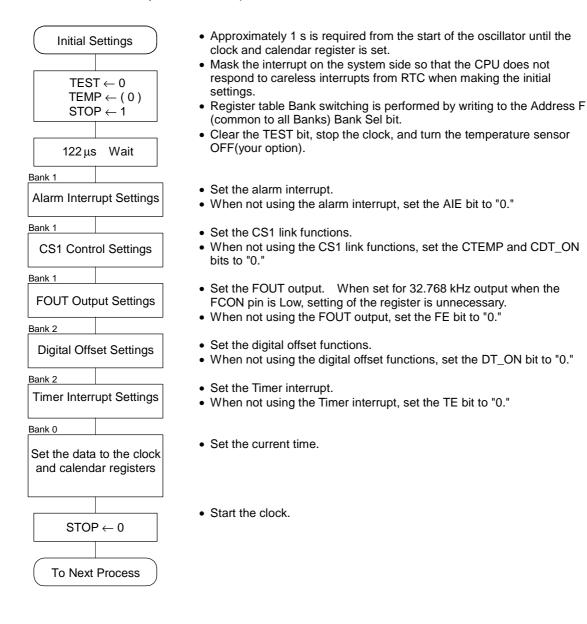

# 7-1. Procedures for initially turning ON the power<sup>\*1</sup> (initial settings)

7-1-1. When a digital pace adjustment function is not used.

\*1 : It is necessary to turn on the power to the RTC first. Once the initial settings for the RTC are completed, the contents are retained in a backup. Therefore when the system power is turned ON again later, perform the "Procedures for recovery from the backup" in the next section.

#### 7-1-2. When used a digital pace adjustment function.

\*1 : It is necessary to turn on the power to the RTC first. Once the initial settings for the RTC are completed, the contents are retained in a backup. Therefore when the system power is turned ON again later, perform the "Procedures for recovery from the backup" in the next section.

| Initial Settings<br>Bank2<br>1) Reg-D(hex) $\leftarrow$ 8(hex)<br>Bank2<br>2) Reg-E(hex) $\leftarrow$ 8(hex)<br>Bank2<br>3) Reg-E(hex) $\leftarrow$ 0(hex)<br>Bank2<br>4) Reg-D(hex) $\leftarrow$ 0(hex)<br>5) STOP $\leftarrow$ 1<br>122 µs Wait<br>Bank 1 | <ul> <li>Approximately 1 s is required from the start of the oscillator until the clock and calendar register is set.</li> <li>Mask the interrupt on the system side so that the CPU does not respond to careless interrupts from RTC when making the initial settings.</li> <li>Register table Bank switching is performed by writing to the Address F (common to all Banks) Bank Sel bit.</li> <li>Please obey faithfully this procedure for initialization of a circuit of digital pace adjustment function and must write data by all means.</li> </ul> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|